- 您現(xiàn)在的位置:買賣IC網 > PDF目錄375483 > C0805C100JDGAC (KEMET Corporation) CERAMIC CHIP / HIGH VOLTAGE PDF資料下載

參數資料

| 型號: | C0805C100JDGAC |

| 廠商: | KEMET Corporation |

| 英文描述: | CERAMIC CHIP / HIGH VOLTAGE |

| 中文描述: | 陶瓷芯片/高電壓 |

| 文件頁數: | 8/9頁 |

| 文件大小: | 1636K |

| 代理商: | C0805C100JDGAC |

KEMET Electronics Corporation, P.O. Box 5928, Greenville, S.C. 29606, (864) 963-6300

20

°

20

°

Maximum

Typical

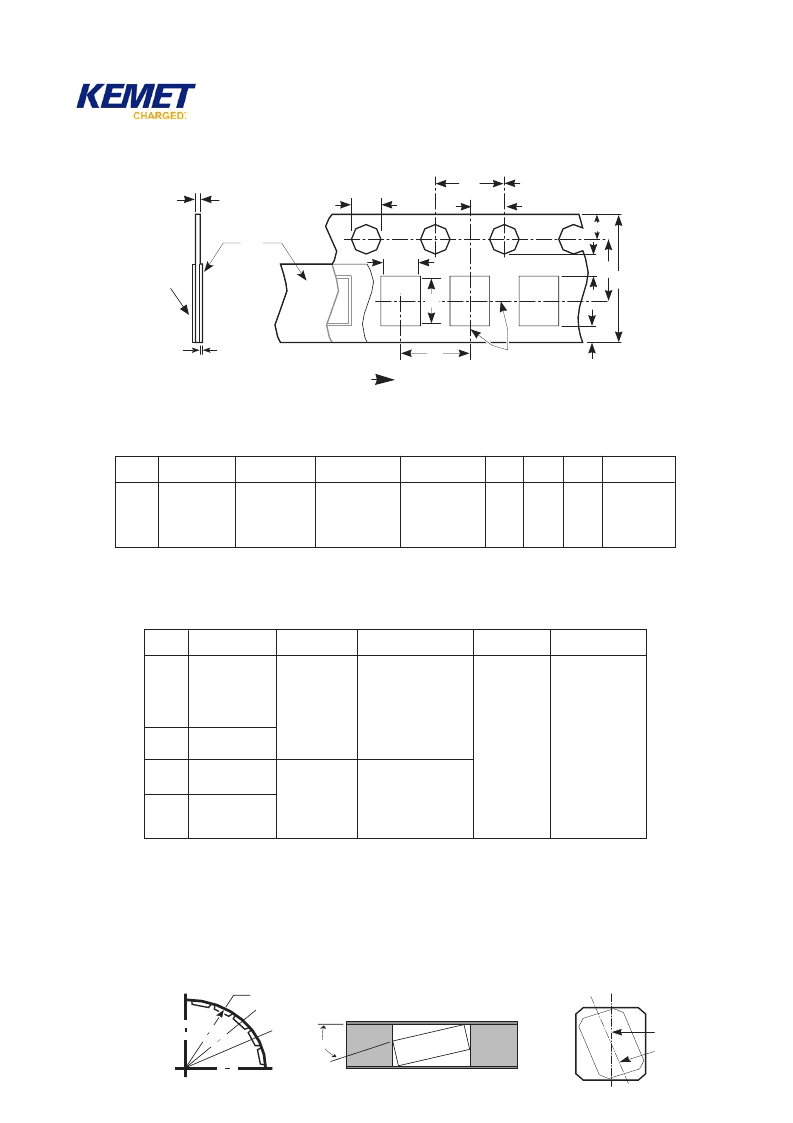

Punched Carrier (Paper Tape) Configuration (Ceramic Chips Only):

Table 1: 8 & 12mm Punched Tape

(

Metric Dimensions Will Govern)

Variable Dimensions - Millimeters (Inches)

Note:

1. A0, B0 and T determined by the maximum dimensions to the ends of the terminals extending from the

body and/or the body dimensions of the component. The clearance between the ends of the terminals or

body of the component to the sides and depth of the cavity (A0, B0 and T) must be within 0.05mm (.002)

minimum and 0.50mm (.020) maximum. The clearance allowed must also prevent rotation of the component

within the cavity of not more than 20 degrees (see sketches A and B).

2. Tape with components shall pass around radius "R" without damage.

3. KEMET nominal thicknesses are: 0402 = 0.6mm and all others 0.95mm minimum.

8mm

and

12mm

1.5

+0.10, -0.0

(.059

+0.004, -0.0)

1.75

±

0.10

(.069

±

0.004)

4.0

±

0.10

(.157

±

0.004)

2.0

±

0.05

(.079

±

0.002)

0.10

(.004)

Max.

0.75

(.030)

Min.

0.75

(.030)

Min.

25 (.984)

See Note 2

Table 1

Tape

Size

D

0

P

0

E

P

2

T

1

G

1

G

2

R Min.

8mm

1/2

Pitch

2.0

±

0.10

(.079

±

.004)

See Require-

ments

Section 3.3 (d)

4.0

±

0.10

(0.157

±

.004)

3.5

±

0.05

(.138

±

.002)

8.0

±

0.3

(.315

±

0.012)

See Note 1

Table 1

1.1mm (.043)

Max. for Paper

Base Tape and

1.6mm (.063)

Max. for Non-

Paper Base

Compositions.

See Note 3.

Tape

Size

P

1

W

F

A

0

B

0

T

8mm

12mm

4.0

±

0.10

(0.157

±

.004)

8.0

±

0.10

(0.315

±

.004)

12mm

Double

Pitch

12.0

±

0.3

(.472

±

.012)

5.5

±

0.05

(.217

±

.002)

Table 1: 8 & 12mm Punched Tape

(

Metric Dimensions Will Govern)

Constant Dimensions - Millimeters (Inches)

Sketch B:

Max. Component

Rotation - Front

Cross Sectional View

Sketch C:

Component Rotation - Top View

A

0

B

0

P

1

P

0

P

2

D

0

F

E

W

Center lines

of cavity

10 pitches cumulative

tolerance on tape

±

0.2 (

±

0.008)

Top

Tape

Cover

T

User Direction of Feed

T

1

Max. Cavity Size

See Note 1

Table 1

Bottom

Tape

Cover

G

2

R

Sketch A:

Bending Radius

See Note 2

Table 1

CERAMIC CHIP CAPACITORS

Packaging Information

96

相關PDF資料 |

PDF描述 |

|---|---|

| C0805C100JDRAC | CERAMIC CHIP / HIGH VOLTAGE |

| C0805C100JFGAC | CERAMIC CHIP / HIGH VOLTAGE |

| C0805C100JFRAC | CERAMIC CHIP / HIGH VOLTAGE |

| C0805C100JGGAC | CERAMIC CHIP / HIGH VOLTAGE |

| C0805C100JGRAC | CERAMIC CHIP / HIGH VOLTAGE |

相關代理商/技術參數 |

參數描述 |

|---|---|

| C0805C100JDGAC7800 | 制造商:KEMET Corporation 功能描述: |

| C0805C100JDGACTU | 功能描述:多層陶瓷電容器MLCC - SMD/SMT 1000volts 10pF 5% C0G RoHS:否 制造商:American Technical Ceramics (ATC) 電容:10 pF 容差:1 % 電壓額定值:250 V 溫度系數/代碼:C0G (NP0) 外殼代碼 - in:0505 外殼代碼 - mm:1414 工作溫度范圍:- 55 C to + 125 C 產品:Low ESR MLCCs 封裝:Reel |

| C0805C100JDRAC | 制造商:KEMET 制造商全稱:Kemet Corporation 功能描述:CERAMIC CHIP / HIGH VOLTAGE |

| C0805C100JFGAC | 制造商:KEMET 制造商全稱:Kemet Corporation 功能描述:CERAMIC CHIP / HIGH VOLTAGE |

| C0805C100JFRAC | 制造商:KEMET 制造商全稱:Kemet Corporation 功能描述:CERAMIC CHIP / HIGH VOLTAGE |

發(fā)布緊急采購,3分鐘左右您將得到回復。