- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄166447 > BP80C31BH (INTEL CORP) 8-BIT, 12 MHz, MICROCONTROLLER, PDIP40 PDF資料下載

參數(shù)資料

| 型號: | BP80C31BH |

| 廠商: | INTEL CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, 12 MHz, MICROCONTROLLER, PDIP40 |

| 封裝: | PLASTIC, DIP-40 |

| 文件頁數(shù): | 13/16頁 |

| 文件大?。?/td> | 842K |

| 代理商: | BP80C31BH |

AUTOMOTIVE 80C31BH/80C51BH/87C51

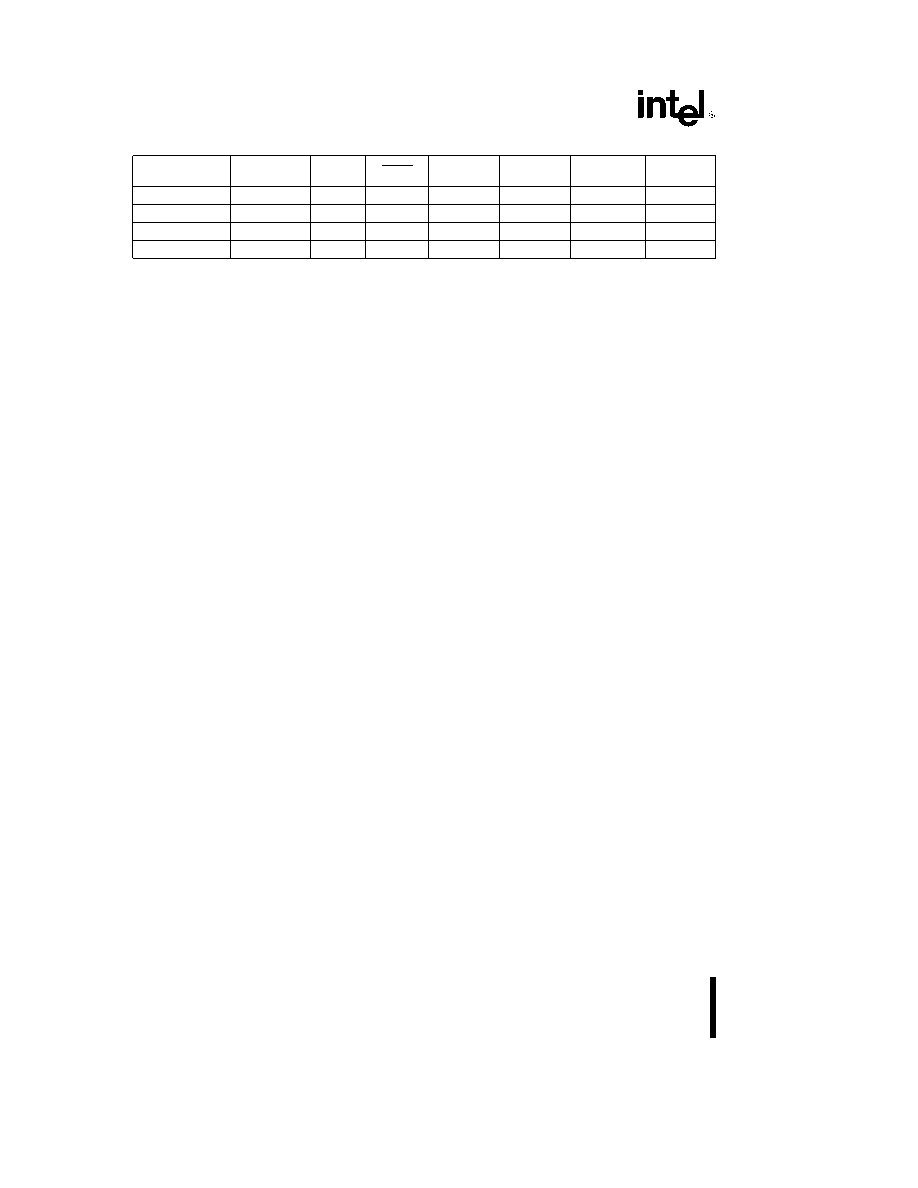

Table 2. Status of the External Pins During Idle and Power Down

Mode

Program

ALE

PSEN

PORT0

PORT1

PORT2

PORT3

Memory

Idle

Internal

1

Data

Idle

External

1

Float

Data

Address

Data

Power Down

Internal

0

Data

Power Down

External

0

Float

Data

NOTE:

For more detailed information on the reduced power modes refer to current Embedded Applications Handbook, and Applica-

tion Note AP-252, ``Designing with the 80C51BH.''

internal RAM in this event, but access to the port

pins is not inhibited. To eliminate the possibility of an

unexpected write to a port pin when Idle is terminat-

ed by reset, the instruction following the one that

invokes Idle should not be one that writes to a port

pin or to external memory.

POWER DOWN MODE

In the Power Down mode the oscillator is stopped,

and the instruction that invokes Power Down is the

last instruction executed. The on-chip RAM and

Special Function Registers retain their values until

the Power Down mode is terminated.

The only exit from Power Down is a hardware reset.

Reset redefines the SFRs but does not change the

on-chip RAM. The reset should not be activated be-

fore VCC is restored to its normal operating level and

must be held active long enough to allow the oscilla-

tor to restart and stabilize.

DESIGN CONSIDERATIONS

At power on, the voltage on VCC and RST must

come up at the same time for a proper start-up.

Before entering the Power Down mode the con-

tents of the Carry Bit and B.7 must be equal.

When the Idle mode is terminated by a hardware

reset, the device normally resumes program exe-

cution, from where it left off, up to two machine

cycles before the internal reset algorithm takes

control. On-chip hardware inhibits access to inter-

nal RAM in this event, but access to the port pins

in not inhibited. To eliminate the possibility of an

unexpected write when Idle is terminated by re-

set, the instruction following the one that invokes

Idle should not be one that writes to a port pin or

to external memory.

An external oscillator may encounter as much as

a 100 pF load at XTAL1 when it starts up. This is

due to interaction between the amplifier and its

feedback capacitance. Once the external signal

meets the VIL and VIH specifications the capaci-

tance will not exceed 20 pF.

For EPROM versions exposure to light when the

device is in operation may cause logic errors. For

this reason, it is suggested that an opaque label

be placed over the window when the die is ex-

posed to ambient light.

6

相關PDF資料 |

PDF描述 |

|---|---|

| BN87C51BH | 8-BIT, OTPROM, 12 MHz, MICROCONTROLLER, PQCC44 |

| BP80C51FA-1 | 8-BIT, 16 MHz, MICROCONTROLLER, PDIP40 |

| BN83C51FA | 8-BIT, MROM, 12 MHz, MICROCONTROLLER, PQCC44 |

| BN80C51FA-1 | 8-BIT, 16 MHz, MICROCONTROLLER, PQCC44 |

| BPF-A410+ | 410 MHz, BAND PASS FILTER |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| BP80C51BH | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

| BP80C51FA | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

| BP8-10 | 制造商:FRONTIER 制造商全稱:Frontier Electronics. 功能描述:8A BRIDGE RECTIFIER |

| BP81003-NFB69LF | 制造商:FCI 功能描述:BP81003-NFB69LF-HF9-218205-001 制造商:FCI 功能描述:BP81003-NFB69LF-HF9-218205-001 - Bulk |

| BP81-12 | 制造商:IDEC CORPORATION 功能描述:Terminal Block |

發(fā)布緊急采購,3分鐘左右您將得到回復。