- 鎮ㄧ従(xi脿n)鍦ㄧ殑浣嶇疆锛�璨疯常IC缍�(w菐ng) > PDF鐩寗4380 > APA600-PQ208A (Microsemi SoC)IC FPGA PROASIC+ 600K 208-PQFP PDF璩囨枡涓嬭級

鍙冩暩(sh霉)璩囨枡

| 鍨嬭櫉锛� | APA600-PQ208A |

| 寤犲晢锛� | Microsemi SoC |

| 鏂囦欢闋佹暩(sh霉)锛� | 90/178闋� |

| 鏂囦欢澶у皬锛� | 0K |

| 鎻忚堪锛� | IC FPGA PROASIC+ 600K 208-PQFP |

| 妯欐簴鍖呰锛� | 24 |

| 绯诲垪锛� | ProASICPLUS |

| RAM 浣嶇附瑷堬細 | 129024 |

| 杓稿叆/杓稿嚭鏁�(sh霉)锛� | 158 |

| 闁€鏁�(sh霉)锛� | 600000 |

| 闆绘簮闆诲锛� | 2.375 V ~ 2.625 V |

| 瀹夎椤炲瀷锛� | 琛ㄩ潰璨艰 |

| 宸ヤ綔婧害锛� | -40°C ~ 125°C |

| 灏佽/澶栨锛� | 208-BFQFP |

| 渚涙噳鍟嗚ō(sh猫)鍌欏皝瑁濓細 | 208-PQFP锛�28x28锛� |

绗�1闋�绗�2闋�绗�3闋�绗�4闋�绗�5闋�绗�6闋�绗�7闋�绗�8闋�绗�9闋�绗�10闋�绗�11闋�绗�12闋�绗�13闋�绗�14闋�绗�15闋�绗�16闋�绗�17闋�绗�18闋�绗�19闋�绗�20闋�绗�21闋�绗�22闋�绗�23闋�绗�24闋�绗�25闋�绗�26闋�绗�27闋�绗�28闋�绗�29闋�绗�30闋�绗�31闋�绗�32闋�绗�33闋�绗�34闋�绗�35闋�绗�36闋�绗�37闋�绗�38闋�绗�39闋�绗�40闋�绗�41闋�绗�42闋�绗�43闋�绗�44闋�绗�45闋�绗�46闋�绗�47闋�绗�48闋�绗�49闋�绗�50闋�绗�51闋�绗�52闋�绗�53闋�绗�54闋�绗�55闋�绗�56闋�绗�57闋�绗�58闋�绗�59闋�绗�60闋�绗�61闋�绗�62闋�绗�63闋�绗�64闋�绗�65闋�绗�66闋�绗�67闋�绗�68闋�绗�69闋�绗�70闋�绗�71闋�绗�72闋�绗�73闋�绗�74闋�绗�75闋�绗�76闋�绗�77闋�绗�78闋�绗�79闋�绗�80闋�绗�81闋�绗�82闋�绗�83闋�绗�84闋�绗�85闋�绗�86闋�绗�87闋�绗�88闋�绗�89闋�鐣跺墠绗�90闋�绗�91闋�绗�92闋�绗�93闋�绗�94闋�绗�95闋�绗�96闋�绗�97闋�绗�98闋�绗�99闋�绗�100闋�绗�101闋�绗�102闋�绗�103闋�绗�104闋�绗�105闋�绗�106闋�绗�107闋�绗�108闋�绗�109闋�绗�110闋�绗�111闋�绗�112闋�绗�113闋�绗�114闋�绗�115闋�绗�116闋�绗�117闋�绗�118闋�绗�119闋�绗�120闋�绗�121闋�绗�122闋�绗�123闋�绗�124闋�绗�125闋�绗�126闋�绗�127闋�绗�128闋�绗�129闋�绗�130闋�绗�131闋�绗�132闋�绗�133闋�绗�134闋�绗�135闋�绗�136闋�绗�137闋�绗�138闋�绗�139闋�绗�140闋�绗�141闋�绗�142闋�绗�143闋�绗�144闋�绗�145闋�绗�146闋�绗�147闋�绗�148闋�绗�149闋�绗�150闋�绗�151闋�绗�152闋�绗�153闋�绗�154闋�绗�155闋�绗�156闋�绗�157闋�绗�158闋�绗�159闋�绗�160闋�绗�161闋�绗�162闋�绗�163闋�绗�164闋�绗�165闋�绗�166闋�绗�167闋�绗�168闋�绗�169闋�绗�170闋�绗�171闋�绗�172闋�绗�173闋�绗�174闋�绗�175闋�绗�176闋�绗�177闋�绗�178闋�

ProASICPLUS Flash Family FPGAs

v5.9

2-9

The TAP controller receives two control inputs (TMS and

TCK) and generates control and clock signals for the rest

of the test logic architecture. On power-up, the TAP

controller enters the Test-Logic-Reset state. To guarantee

a reset of the controller from any of the possible states,

TMS must remain high for five TCK cycles. The TRST pin

may also be used to asynchronously place the TAP

controller in the Test-Logic-Reset state.

ProASICPLUS devices support three types of test data

registers: bypass, device identification, and boundary

scan. The bypass register is selected when no other

register needs to be accessed in a device. This speeds up

test data transfer to other devices in a test data path.

The 32-bit device identification register is a shift register

with four fields (lowest significant byte (LSB), ID number,

part number and version). The boundary-scan register

observes and controls the state of each I/O pin.

Each I/O cell has three boundary-scan register cells, each

with a serial-in, serial-out, parallel-in, and parallel-out

pin. The serial pins are used to serially connect all the

boundary-scan register cells in a device into a boundary-

scan register chain, which starts at the TDI pin and ends

at the TDO pin. The parallel ports are connected to the

internal core logic tile and the input, output, and control

ports of an I/O buffer to capture and load data into the

register to control or observe the logic state of each I/O.

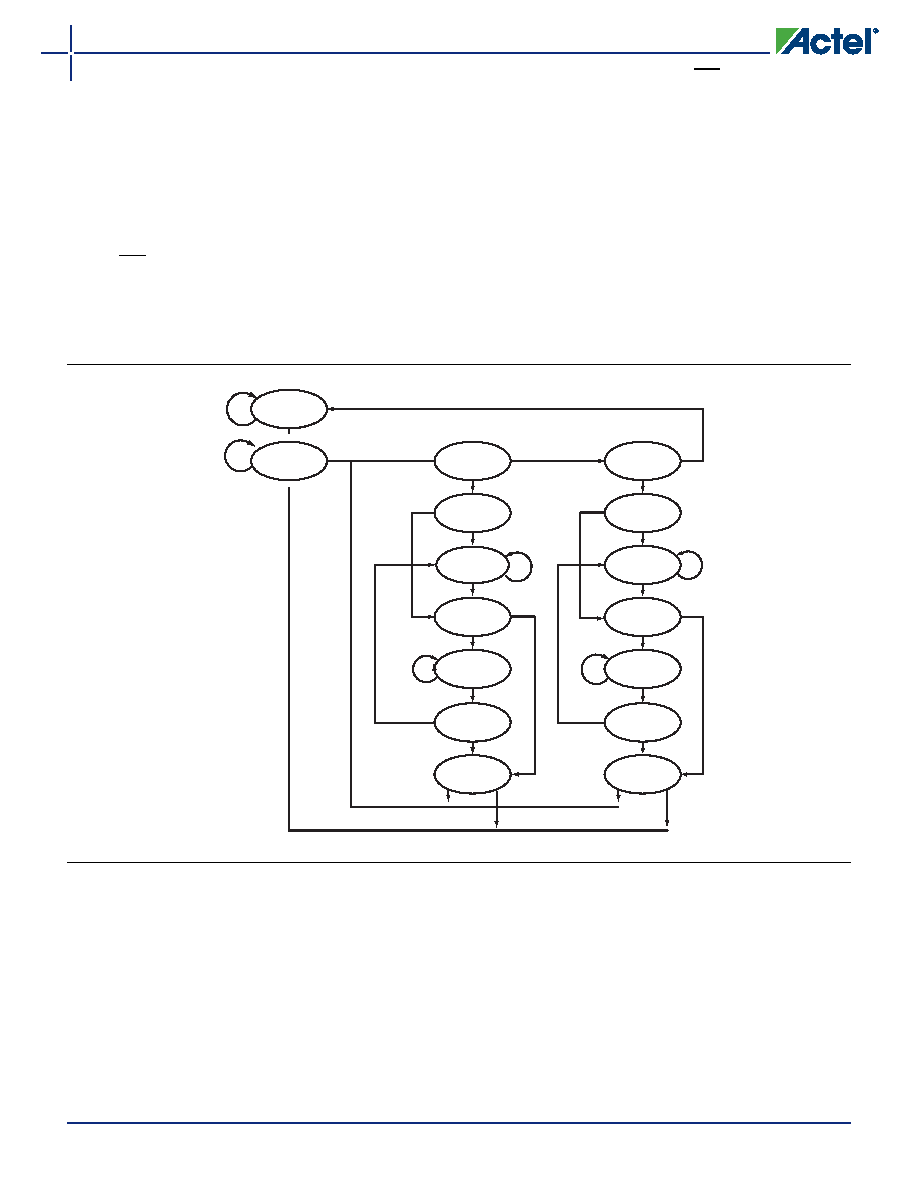

Figure 2-10 TAP Controller State Diagram

Test-Logic

Reset

Run-Test/

Idle

Select-DR-

Scan

Capture-DR

Shift-DR

Exit-DR

Pause-DR

Exit2-DR

Update-DR

Select-IR-

Scan

Capture-IR

Shift-IR

Exit-IR

Pause-IR

Exit2-IR

Update-IR

1

0

1

0

00

1

00

1

0

1

0

鐩搁棞(gu膩n)PDF璩囨枡 |

PDF鎻忚堪 |

|---|---|

| GBB106DHAR-S621 | CONN EDGECARD 212PS R/A .050 SLD |

| IDT71V416S10PHG | IC SRAM 4MBIT 10NS 44TSOP |

| APA600-PQG208A | IC FPGA PROASIC+ 600K 208-PQFP |

| RSA50DRMD-S273 | CONN EDGECARD 100POS .125 SQ WW |

| APA600-BG456I | IC FPGA PROASIC+ 600K 456-PBGA |

鐩搁棞(gu膩n)浠g悊鍟�/鎶€琛�(sh霉)鍙冩暩(sh霉) |

鍙冩暩(sh霉)鎻忚堪 |

|---|---|

| APA600-PQ208I | 鍔熻兘鎻忚堪:IC FPGA PROASIC+ 600K 208-PQFP RoHS:鍚� 椤炲垾:闆嗘垚闆昏矾 (IC) >> 宓屽叆寮� - FPGA锛堢従(xi脿n)鍫村彲绶ㄧ▼闁€闄e垪锛� 绯诲垪:ProASICPLUS 鐢�(ch菐n)鍝佸煿瑷撴ā濉�:Three Reasons to Use FPGA's in Industrial Designs Cyclone IV FPGA Family Overview 鐗硅壊鐢�(ch菐n)鍝�:Cyclone? IV FPGAs 妯欐簴鍖呰:60 绯诲垪:CYCLONE® IV GX LAB/CLB鏁�(sh霉):9360 閭忚集鍏冧欢/鍠厓鏁�(sh霉):149760 RAM 浣嶇附瑷�:6635520 杓稿叆/杓稿嚭鏁�(sh霉):270 闁€鏁�(sh霉):- 闆绘簮闆诲:1.16 V ~ 1.24 V 瀹夎椤炲瀷:琛ㄩ潰璨艰 宸ヤ綔婧害:0°C ~ 85°C 灏佽/澶栨:484-BGA 渚涙噳鍟嗚ō(sh猫)鍌欏皝瑁�:484-FBGA锛�23x23锛� |

| APA600-PQ208M | 鍒堕€犲晢:Microsemi Corporation 鍔熻兘鎻忚堪:FPGA ProASICPLUS Family 600K Gates 180MHz 0.22um (CMOS) Technology 2.5V 208-Pin PQFP 鍒堕€犲晢:Microsemi Corporation 鍔熻兘鎻忚堪:FPGA PROASICPLUS 600K GATES 180MHZ 0.22UM 2.5V 208PQFP - Trays 鍒堕€犲晢:Microsemi SOC Products Group 鍔熻兘鎻忚堪:FPGA PROASICPLUS 600K GATES 180MHZ 0.22UM 2.5V 208PQFP - Trays |

| APA600-PQ896A | 鍒堕€犲晢:ACTEL 鍒堕€犲晢鍏ㄧū:Actel Corporation 鍔熻兘鎻忚堪:Automotive-Grade ProASIC Flash Family FPGAs |

| APA600-PQB | 鍒堕€犲晢:ACTEL 鍒堕€犲晢鍏ㄧū:Actel Corporation 鍔熻兘鎻忚堪:ProASIC Flash Family FPGAs |

| APA600-PQES | 鍒堕€犲晢:ACTEL 鍒堕€犲晢鍏ㄧū:Actel Corporation 鍔熻兘鎻忚堪:ProASIC Flash Family FPGAs |

鐧�(f膩)甯冪穵鎬ラ噰璩�锛�3鍒嗛悩宸﹀彸鎮ㄥ皣寰楀埌鍥炲京銆�