- 鎮ㄧ従(xi脿n)鍦ㄧ殑浣嶇疆锛�璨疯常IC缍�(w菐ng) > PDF鐩寗4334 > APA300-CQ352B (Microsemi SoC)IC FPGA PROASIC+ 300K 352-CQFP PDF璩囨枡涓嬭級

鍙冩暩(sh霉)璩囨枡

| 鍨嬭櫉(h脿o)锛� | APA300-CQ352B |

| 寤犲晢锛� | Microsemi SoC |

| 鏂囦欢闋佹暩(sh霉)锛� | 99/178闋� |

| 鏂囦欢澶�?銆�?/td> | 0K |

| 鎻忚堪锛� | IC FPGA PROASIC+ 300K 352-CQFP |

| 妯�(bi膩o)婧�(zh菙n)鍖呰锛� | 1 |

| 绯诲垪锛� | ProASICPLUS |

| RAM 浣嶇附瑷�(j矛)锛� | 73728 |

| 杓稿叆/杓稿嚭鏁�(sh霉)锛� | 248 |

| 闁€鏁�(sh霉)锛� | 300000 |

| 闆绘簮闆诲锛� | 2.3 V ~ 2.7 V |

| 瀹夎椤炲瀷锛� | 琛ㄩ潰璨艰 |

| 灏佽/澶栨锛� | 352-BFCQFP锛屽付鎷夋】 |

| 渚涙噳(y墨ng)鍟嗚ō(sh猫)鍌欏皝瑁濓細 | 352-CQFP锛�75x75锛� |

绗�1闋�绗�2闋�绗�3闋�绗�4闋�绗�5闋�绗�6闋�绗�7闋�绗�8闋�绗�9闋�绗�10闋�绗�11闋�绗�12闋�绗�13闋�绗�14闋�绗�15闋�绗�16闋�绗�17闋�绗�18闋�绗�19闋�绗�20闋�绗�21闋�绗�22闋�绗�23闋�绗�24闋�绗�25闋�绗�26闋�绗�27闋�绗�28闋�绗�29闋�绗�30闋�绗�31闋�绗�32闋�绗�33闋�绗�34闋�绗�35闋�绗�36闋�绗�37闋�绗�38闋�绗�39闋�绗�40闋�绗�41闋�绗�42闋�绗�43闋�绗�44闋�绗�45闋�绗�46闋�绗�47闋�绗�48闋�绗�49闋�绗�50闋�绗�51闋�绗�52闋�绗�53闋�绗�54闋�绗�55闋�绗�56闋�绗�57闋�绗�58闋�绗�59闋�绗�60闋�绗�61闋�绗�62闋�绗�63闋�绗�64闋�绗�65闋�绗�66闋�绗�67闋�绗�68闋�绗�69闋�绗�70闋�绗�71闋�绗�72闋�绗�73闋�绗�74闋�绗�75闋�绗�76闋�绗�77闋�绗�78闋�绗�79闋�绗�80闋�绗�81闋�绗�82闋�绗�83闋�绗�84闋�绗�85闋�绗�86闋�绗�87闋�绗�88闋�绗�89闋�绗�90闋�绗�91闋�绗�92闋�绗�93闋�绗�94闋�绗�95闋�绗�96闋�绗�97闋�绗�98闋�鐣�(d膩ng)鍓嶇99闋�绗�100闋�绗�101闋�绗�102闋�绗�103闋�绗�104闋�绗�105闋�绗�106闋�绗�107闋�绗�108闋�绗�109闋�绗�110闋�绗�111闋�绗�112闋�绗�113闋�绗�114闋�绗�115闋�绗�116闋�绗�117闋�绗�118闋�绗�119闋�绗�120闋�绗�121闋�绗�122闋�绗�123闋�绗�124闋�绗�125闋�绗�126闋�绗�127闋�绗�128闋�绗�129闋�绗�130闋�绗�131闋�绗�132闋�绗�133闋�绗�134闋�绗�135闋�绗�136闋�绗�137闋�绗�138闋�绗�139闋�绗�140闋�绗�141闋�绗�142闋�绗�143闋�绗�144闋�绗�145闋�绗�146闋�绗�147闋�绗�148闋�绗�149闋�绗�150闋�绗�151闋�绗�152闋�绗�153闋�绗�154闋�绗�155闋�绗�156闋�绗�157闋�绗�158闋�绗�159闋�绗�160闋�绗�161闋�绗�162闋�绗�163闋�绗�164闋�绗�165闋�绗�166闋�绗�167闋�绗�168闋�绗�169闋�绗�170闋�绗�171闋�绗�172闋�绗�173闋�绗�174闋�绗�175闋�绗�176闋�绗�177闋�绗�178闋�

ProASICPLUS Flash Family FPGAs

v5.9

2-17

Logic Tile Timing Characteristics

Timing characteristics for ProASICPLUS devices fall into

three categories: family dependent, device dependent,

and design dependent. The input and output buffer

characteristics are common to all ProASICPLUS family

members. Internal routing delays are device dependent.

Design dependency means that actual delays are not

determined until after placement and routing of the

user鈥檚 design are complete. Delay values may then be

determined by using the Timer utility or by performing

simulation with post-layout delays.

Critical Nets and Typical Nets

Propagation delays are expressed only for typical nets,

which are used for initial design performance evaluation.

Critical net delays can then be applied to the most

timing-critical paths. Critical nets are determined by net

property assignment prior to place-and-route. Refer to

the Actel Designer User鈥檚 Guide or online help for details

on using constraints.

Timing Derating

Since ProASICPLUS devices are manufactured with a

CMOS process, device performance will vary with

temperature, voltage, and process. Minimum timing

parameters

reflect

maximum

operating

voltage,

minimum operating temperature, and optimal process

variations. Maximum timing parameters reflect minimum

operating voltage, maximum operating temperature,

and

worst-case

process

variations

(within

process

specifications). The derating factors shown in Table 2-9

should be applied to all timing data contained within

this datasheet.

All timing numbers listed in this datasheet represent

sample timing characteristics of ProASICPLUS devices.

Actual timing delay values are design-specific and can be

derived from the Timer tool in Actel鈥檚 Designer software

after place-and-route.

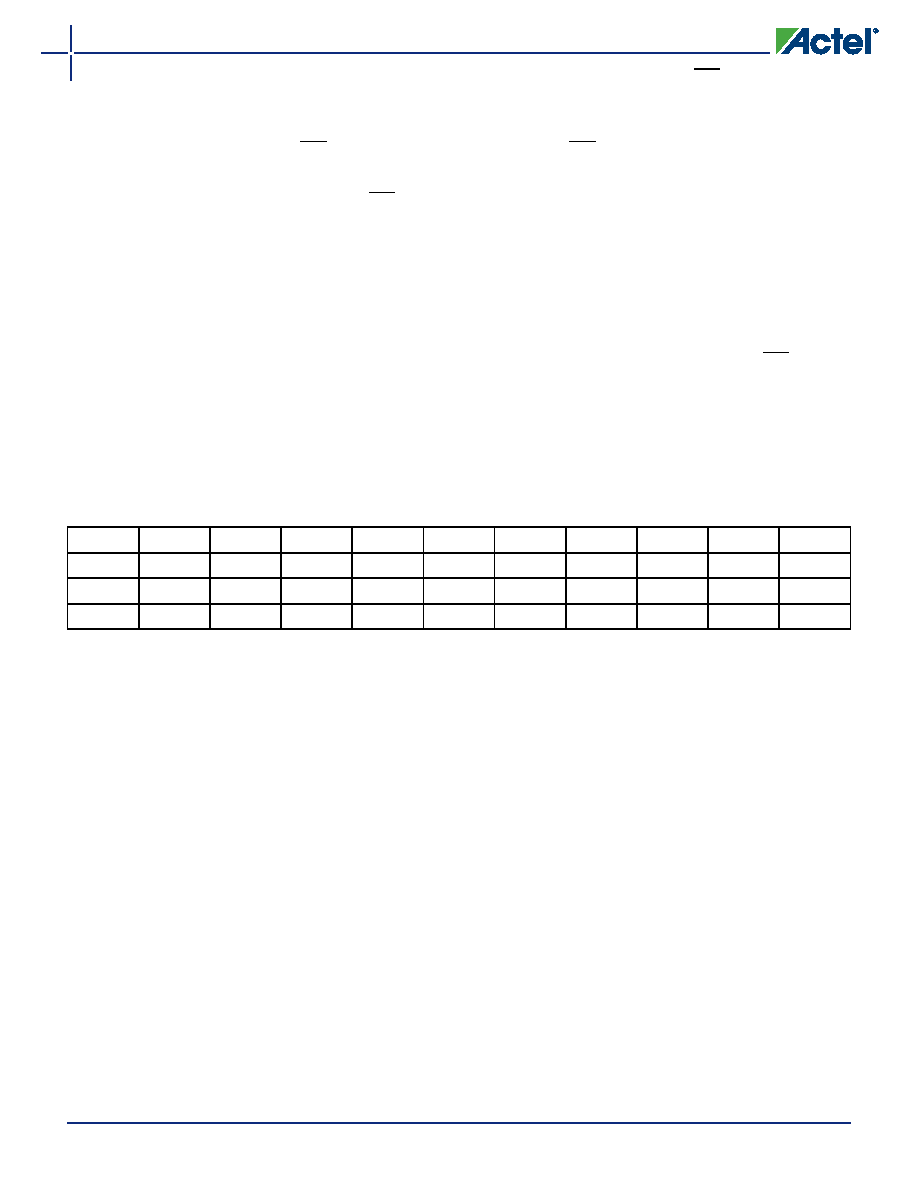

Table 2-9

Temperature and Voltage Derating Factors

(Normalized to Worst-Case Commercial, TJ = 70掳C, VDD = 2.3 V)

鈥�55掳C

鈥�40掳C

0掳C

25掳C

70掳C

85掳C

110掳C

125掳C

135掳C

150掳C

2.3 V

0.84

0.860.910.941.001.021.05

1.13

1.181.27

2.5 V

0.81

0.820.870.900.950.981.01

1.09

1.131.21

2.7 V

0.77

0.790.830.860.910.930.96

1.04

1.081.16

Notes:

1. The user can set the junction temperature in Designer software to be any integer value in the range of 鈥�55掳C to 175掳C.

2. The user can set the core voltage in Designer software to be any value between 1.4 V and 1.6 V.

鐩搁棞(gu膩n)PDF璩囨枡 |

PDF鎻忚堪 |

|---|---|

| A42MX36-CQ256 | IC FPGA MX SGL CHIP 54K 256-CQFP |

| 93C46AT-I/ST | IC EEPROM 1KBIT 2MHZ 8TSSOP |

| EP2AGX260FF35C6 | IC ARRIA II GX 260K 1152FBGA |

| EP2AGX190FF35I5N | IC ARRIA II GX 190K 1152FBGA |

| EP2AGX190FF35C4N | IC ARRIA II GX 190K 1152FBGA |

鐩搁棞(gu膩n)浠g悊鍟�/鎶€琛�(sh霉)鍙冩暩(sh霉) |

鍙冩暩(sh霉)鎻忚堪 |

|---|---|

| APA300-CQ352M | 鍒堕€犲晢:Microsemi Corporation 鍔熻兘鎻忚堪:FPGA PROASICPLUS 300K GATES 180MHZ 0.22UM 2.5V 352CQFP - Trays 鍒堕€犲晢:Microsemi Corporation 鍔熻兘鎻忚堪:IC FPGA PROASIC+ 300K 352CQFP 鍒堕€犲晢:Microsemi Corporation 鍔熻兘鎻忚堪:IC FPGA 248 I/O 352CQFP |

| APA300-CQB | 鍒堕€犲晢:ACTEL 鍒堕€犲晢鍏ㄧū:Actel Corporation 鍔熻兘鎻忚堪:ProASIC Flash Family FPGAs |

| APA300-CQES | 鍒堕€犲晢:ACTEL 鍒堕€犲晢鍏ㄧū:Actel Corporation 鍔熻兘鎻忚堪:ProASIC Flash Family FPGAs |

| APA300-CQGB | 鍒堕€犲晢:ACTEL 鍒堕€犲晢鍏ㄧū:Actel Corporation 鍔熻兘鎻忚堪:ProASIC Flash Family FPGAs |

| APA300-CQGES | 鍒堕€犲晢:ACTEL 鍒堕€犲晢鍏ㄧū:Actel Corporation 鍔熻兘鎻忚堪:ProASIC Flash Family FPGAs |

鐧�(f膩)甯冪穵鎬ラ噰璩�锛�3鍒嗛悩宸﹀彸鎮ㄥ皣寰楀埌鍥炲京(f霉)銆�