- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375308 > AM49PDL640AG85NT (SPANSION LLC) 64 Megabit (4 M x 16-Bit) CMOS 3.0 Volt-only, Simultaneous Operation Flash Memory and 16 Mbit (1 M x 16-Bit) Pseudo Static RAM PDF資料下載

參數(shù)資料

| 型號: | AM49PDL640AG85NT |

| 廠商: | SPANSION LLC |

| 元件分類: | 存儲器 |

| 英文描述: | 64 Megabit (4 M x 16-Bit) CMOS 3.0 Volt-only, Simultaneous Operation Flash Memory and 16 Mbit (1 M x 16-Bit) Pseudo Static RAM |

| 中文描述: | SPECIALTY MEMORY CIRCUIT, PBGA73 |

| 封裝: | 13 X 9 MM, FBGA-73 |

| 文件頁數(shù): | 4/69頁 |

| 文件大?。?/td> | 491K |

| 代理商: | AM49PDL640AG85NT |

第1頁第2頁第3頁當(dāng)前第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁

2

Am49PDL640AG

November 20, 2003

P R E L I M I N A R Y

GENERAL DESCRIPTION

Am29PDL640G Features

The Am29PDL640G is a 64 Mbit, 3.0 volt-only Page Mode

and Simultaneous Read/Write Flash memory device orga-

nized as 4 Mwords. The device is offered in 73-ball

Fine-pitch BGA packages. The word-wide data (x16) ap-

pears on DQ15-DQ0. This device can be programmed

in-system or in standard EPROM programmers. A 12.0 V

V

PP

is not required for write or erase operations.

The device offers fast page access times of 25, 30, and 45

ns, with corresponding random access times of 65, 70, 85,

and 90 ns, respectively, allowing high speed microproces-

sors to operate without wait states. To eliminate bus conten-

tion the device has separate chip enable (CE#), write enable

(WE#) and output enable (OE#) controls.

Simultaneous Read/Write Operation with

Zero Latency

The Simultaneous Read/Write architecture provides

simul-

taneous operation

by dividing the memory space into 4

banks, which can be considered to be four separate memory

arrays as far as certain operations are concerned. The de-

vice can improve overall system performance by allowing a

host system to program or erase in one bank, then immedi-

ately and simultaneously read from another bank with zero

latency (with two simultaneous operations operating at any

one time). This releases the system from waiting for the

completion of a program or erase operation, greatly improv-

ing system performance.

The device can be organized in both top and bottom sector

configurations. The banks are organized as follows:

Page Mode Features

The device is AC timing, input/output, and package

compat-

ible with 4 Mbit x16 page mode mask ROM

. The page size

is 8 words.

After initial page access is accomplished, the page mode op-

eration provides fast read access speed of random locations

within that page.

Standard Flash Memory Features

The device requires a

single 3.0 volt power supply

(2.7 V

to 3.1 V) for both read and write functions. Internally gener-

ated and regulated voltages are provided for the program

and erase operations.

The device is entirely command set compatible with the

JEDEC 42.4 single-power-supply Flash standard

. Com-

mands are written to the command register using standard

microprocessor write timing. Register contents serve as in-

puts to an internal state-machine that controls the erase and

programming circuitry. Write cycles also internally latch ad-

dresses and data needed for the programming and erase

operations. Reading data out of the device is similar to read-

ing from other Flash or EPROM devices.

Device programming occurs by executing the program com-

mand sequence. The Unlock Bypass mode facilitates faster

programming times by requiring only two write cycles to pro-

gram data instead of four. Device erasure occurs by execut-

ing the erase command sequence.

The host system can detect whether a program or erase op-

eration is complete by reading the DQ7 (Data# Polling) and

DQ6 (toggle)

status bits

. After a program or erase cycle has

been completed, the device is ready to read array data or ac-

cept another command.

The sector erase architecture allows memory sectors to be

erased and reprogrammed without affecting the data con-

tents of other sectors. The device is fully erased when

shipped from the factory.

Hardware data protection

measures include a low V

CC

de-

tector that automatically inhibits write operations during

power transitions. The hardware sector protection feature

disables both program and erase operations in any combina-

tion of sectors of memory. This can be achieved in-system or

via programming equipment.

The Erase Suspend/Erase Resume

feature enables the

user to put erase on hold for any period of time to read data

from, or program data to, any sector that is not selected for

erasure. True background erase can thus be achieved. If a

read is needed from the SecSi Sector area (One Time Pro-

gram area) after an erase suspend, then the user must use

the proper command sequence to enter and exit this region.

The device offers two power-saving features. When ad-

dresses have been stable for a specified amount of time, the

device enters the

automatic sleep mode

. The system can

also place the device into the standby mode. Power con-

sumption is greatly reduced in both these modes.

AMD’s Flash technology combined years of Flash memory

manufacturing experience to produce the highest levels of

quality, reliability and cost effectiveness. The device electri-

cally erases all bits within a sector simultaneously via

Fowler-Nordheim tunneling. The data is programmed using

hot electron injection.

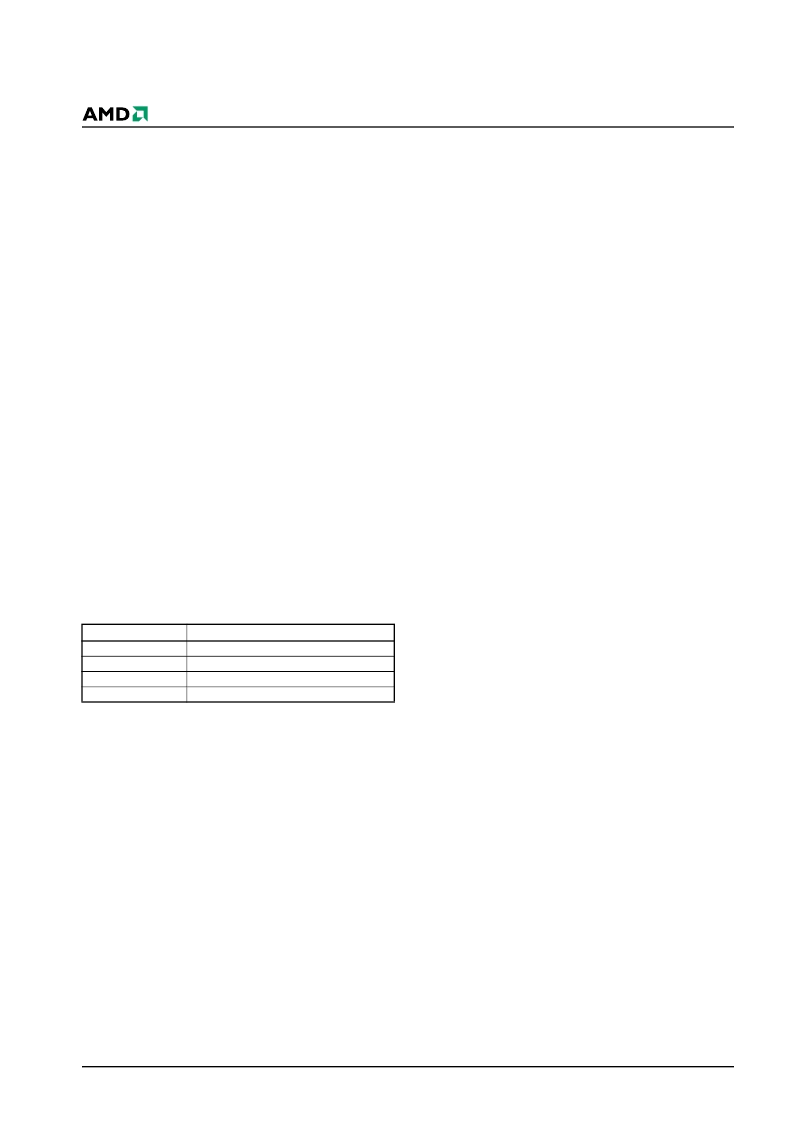

Bank

A

B

C

D

Sectors

8 Mbit (4 Kw x 8 and 32 Kw x 15)

24 Mbit (32 Kw x 48)

24 Mbit (32 Kw x 48)

8 Mbit (4 Kw x 8 and 32 Kw x 15)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AM49PDL640AGA70NS | 64 Megabit (4 M x 16-Bit) CMOS 3.0 Volt-only, Simultaneous Operation Flash Memory and 16 Mbit (1 M x 16-Bit) Pseudo Static RAM |

| AM49PDL640AGA70NT | 64 Megabit (4 M x 16-Bit) CMOS 3.0 Volt-only, Simultaneous Operation Flash Memory and 16 Mbit (1 M x 16-Bit) Pseudo Static RAM |

| AM50-0003 | LJT 128C 128#22D SKT WALL RECP |

| AM50-0003RTR | LJT 128C 128#22D SKT WALL RECP |

| AM50-0003SMB | High Dynamic Range Low Noise Amplifier 800-1000 MHz |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AM49PDL640AGA70NS | 制造商:SPANSION 制造商全稱:SPANSION 功能描述:64 Megabit (4 M x 16-Bit) CMOS 3.0 Volt-only, Simultaneous Operation Flash Memory and 16 Mbit (1 M x 16-Bit) Pseudo Static RAM |

| AM49PDL640AGA70NT | 制造商:SPANSION 制造商全稱:SPANSION 功能描述:64 Megabit (4 M x 16-Bit) CMOS 3.0 Volt-only, Simultaneous Operation Flash Memory and 16 Mbit (1 M x 16-Bit) Pseudo Static RAM |

| AM4-A2-A-30-3 | 制造商:HEINEMANN / EATON 功能描述: |

| AM4-A3-A-30-30-30-15-2 | 制造商:HEINEMANN / EATON 功能描述: |

| AM4-A8-A-60-10 | 制造商:HEINEMANN / EATON 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。