- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375307 > AM49LV128BML15NS (SPANSION LLC) 128 Megabit (8 M x 16-Bit) MirrorBit⑩ Uniform Sector Flash Memory and 32 Mbit (2 M x 16-Bit) PDF資料下載

參數(shù)資料

| 型號(hào): | AM49LV128BML15NS |

| 廠商: | SPANSION LLC |

| 元件分類: | 存儲(chǔ)器 |

| 英文描述: | 128 Megabit (8 M x 16-Bit) MirrorBit⑩ Uniform Sector Flash Memory and 32 Mbit (2 M x 16-Bit) |

| 中文描述: | SPECIALTY MEMORY CIRCUIT, PBGA64 |

| 封裝: | 12 X 9 MM, FBGA-64 |

| 文件頁(yè)數(shù): | 62/98頁(yè) |

| 文件大?。?/td> | 1016K |

| 代理商: | AM49LV128BML15NS |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)當(dāng)前第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)

60

Am49LV128BM

June 17, 2004

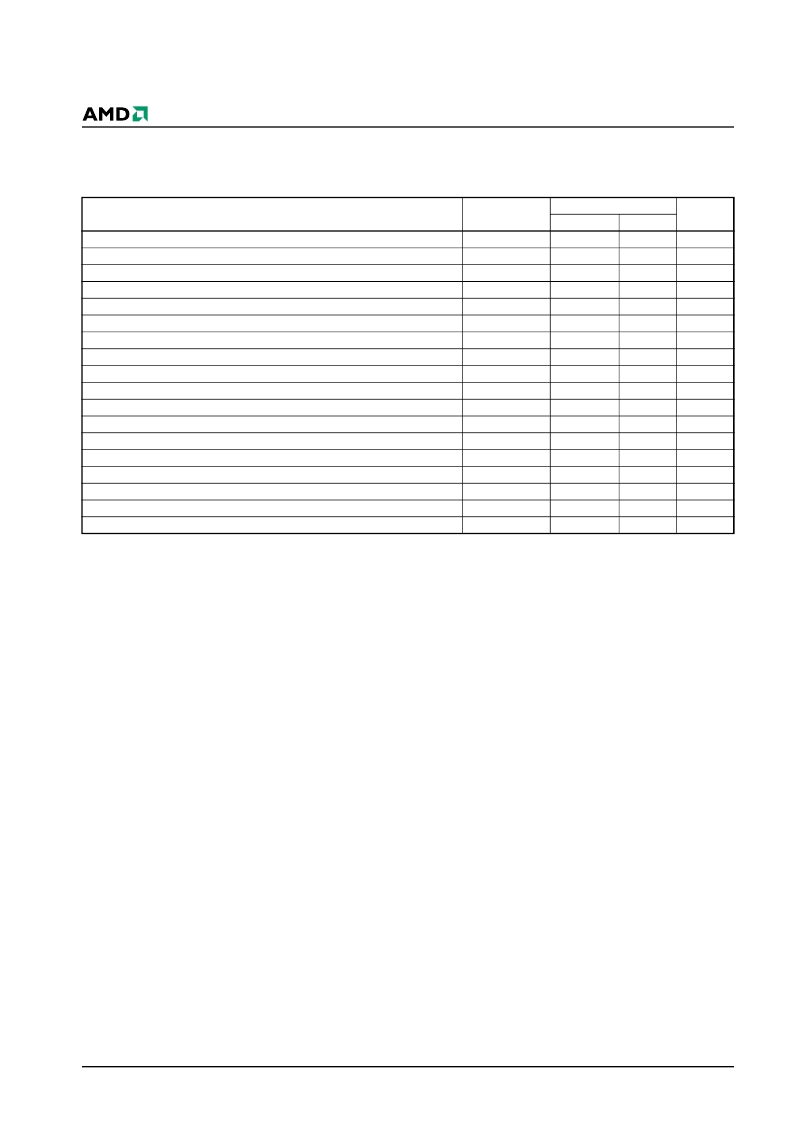

PSRAM AC CHARACTERISTICS

Write Operation

Notes:

1. Maximum value is applicable if CE1# is kept at Low

without any address change.

2. Minimum value must be equal or greater than the sum of

write pulse (t

CW

, T

WP

, T

BW

) and write recovery time (t

WCR

,

T

WR

or t

BR

).

3. Write pulse is defined from High to Low transition of CE1#,

WE#, or LB#/UB#, whichever occurs last.

4. Applicable for byte mask only. Byte mask setup time is

defined to the High to Low transition of CE1# or WE#

whichever occurs last.

5. Applicable for byte mask only. Byte mask hold time is

defined from the Low to High transition of CE1# or WE#

whichever occurs first.

6. Write recovery is defined from Low to High transition of

CE1#, WE#, or LB#/UB#, whichever occurs first.

7. If OE# is Low after minimum t

OHCL

, read cycle is initiated. In

other words, OE# must be brought to High within 5 ns after

CE1# is brought to Low. Once read cycle is initiated, new

write pulse should be input after minimum t

RC

is met

8. If OE# is Low after new address input, read cycle is

initiated. In other words, OE# must be brought to High at

the same time or before new address valid. Once read

cycle is initiated, new write pulse should be input after

minimum t

RC

is met and data bus is in High-Z

9. Absolute minimum values and defined at minimum V

IH

level.

10. If the actual value of t

WHOL

is shorter than the specified

minimum values, the actual t

AA

of following Read may

become longer by the amount of subtracting the actual

value from the specified minimum value.

Parameter

Symbol

t

WC

t

AS

t

CW

t

WP

t

BW

t

BS

t

BH

t

WRC

t

WR

t

BR

t

DS

t

DH

t

OHCL

t

OES

t

WHOL

t

BWO

t

CP

t

AH

Value

Unit

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

10

ns

ns

ns

Min.

65

0

40

40

40

-5

-5

12

7.5

12

12

0

-5

0

12

30

12

0

Max.

1000

–

–

–

–

–

–

–

1000

1000

–

–

–

–

–

–

–

–

Write Cycle Time (Notes 1, 2)

Address Setup Time (Note 3)

CE1# Write Pulse Width (Note 3)

WE# Write Pulse Width (Note 3)

LB#/UB# Write Pulse Width (Note 3)

LB#/UB# Byte Mask Setup Time (Note 4)

LB#/UB# Byte Mask Hold Time (Note 5)

CE1# Write Recovery Time (Note 6)

WE# Write Recovery Time (Note 6)

LB#/UB# Write Recovery Time (Note 6)

Data Setup Time

Data Hold Time

OE# High to CE1# Low Setup Time for Write (Note 7)

OE# High to Address Setup Time for Write (Note 8)

WE#/UB#/LB# High to OE# Low Setup Time for Read (Note 10)

LB# and UB# Write Pulse Overlap

CE1# High Pulse Width

Address Hold Time for Write End (Note 3)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AM49LV128BML15NT | 128 Megabit (8 M x 16-Bit) MirrorBit⑩ Uniform Sector Flash Memory and 32 Mbit (2 M x 16-Bit) |

| AM49LV6408M | Stacked Multi-chip Package (MCP) 64 Mbit (4 M x 16 bit) Flash Memory and 8 Mbit (512K x 16-Bit) |

| AM49LV6408MB10IT | Stacked Multi-chip Package (MCP) 64 Mbit (4 M x 16 bit) Flash Memory and 8 Mbit (512K x 16-Bit) |

| AM49LV6408MB11IT | Stacked Multi-chip Package (MCP) 64 Mbit (4 M x 16 bit) Flash Memory and 8 Mbit (512K x 16-Bit) |

| AM49LV6408MB15IT | Stacked Multi-chip Package (MCP) 64 Mbit (4 M x 16 bit) Flash Memory and 8 Mbit (512K x 16-Bit) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AM49LV128BML15NT | 制造商:SPANSION 制造商全稱:SPANSION 功能描述:128 Megabit (8 M x 16-Bit) MirrorBit⑩ Uniform Sector Flash Memory and 32 Mbit (2 M x 16-Bit) |

| AM49LV4608M | 制造商:SPANSION 制造商全稱:SPANSION 功能描述:Stacked Multi-chip Package (MCP) 64 Mbit (4 M x 16 bit) Flash Memory and 8 Mbit (512K x 16-Bit) pseudo Static RAM |

| AM49LV4608MB10IS | 制造商:SPANSION 制造商全稱:SPANSION 功能描述:Stacked Multi-chip Package (MCP) 64 Mbit (4 M x 16 bit) Flash Memory and 8 Mbit (512K x 16-Bit) pseudo Static RAM |

| AM49LV4608MB10IT | 制造商:SPANSION 制造商全稱:SPANSION 功能描述:Stacked Multi-chip Package (MCP) 64 Mbit (4 M x 16 bit) Flash Memory and 8 Mbit (512K x 16-Bit) pseudo Static RAM |

| AM49LV4608MB11IS | 制造商:SPANSION 制造商全稱:SPANSION 功能描述:Stacked Multi-chip Package (MCP) 64 Mbit (4 M x 16 bit) Flash Memory and 8 Mbit (512K x 16-Bit) pseudo Static RAM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。