- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375307 > AM49LV128BMAL15NT (SPANSION LLC) 128 Megabit (8 M x 16-Bit) MirrorBit⑩ Uniform Sector Flash Memory and 32 Mbit (2 M x 16-Bit) PDF資料下載

參數(shù)資料

| 型號(hào): | AM49LV128BMAL15NT |

| 廠商: | SPANSION LLC |

| 元件分類: | 存儲(chǔ)器 |

| 英文描述: | 128 Megabit (8 M x 16-Bit) MirrorBit⑩ Uniform Sector Flash Memory and 32 Mbit (2 M x 16-Bit) |

| 中文描述: | SPECIALTY MEMORY CIRCUIT, PBGA64 |

| 封裝: | 12 X 9 MM, FBGA-64 |

| 文件頁數(shù): | 58/98頁 |

| 文件大小: | 1016K |

| 代理商: | AM49LV128BMAL15NT |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁當(dāng)前第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁

56

Am49LV128BM

June 17, 2004

POWER DOWN

Power Down

The Power Down is to enter low power idle state when

CE2 stays Low. The pSRAM has two power down

modes, Deep Sleep and 8M Partial. These can be pro-

grammed by series of read/write operation. See the

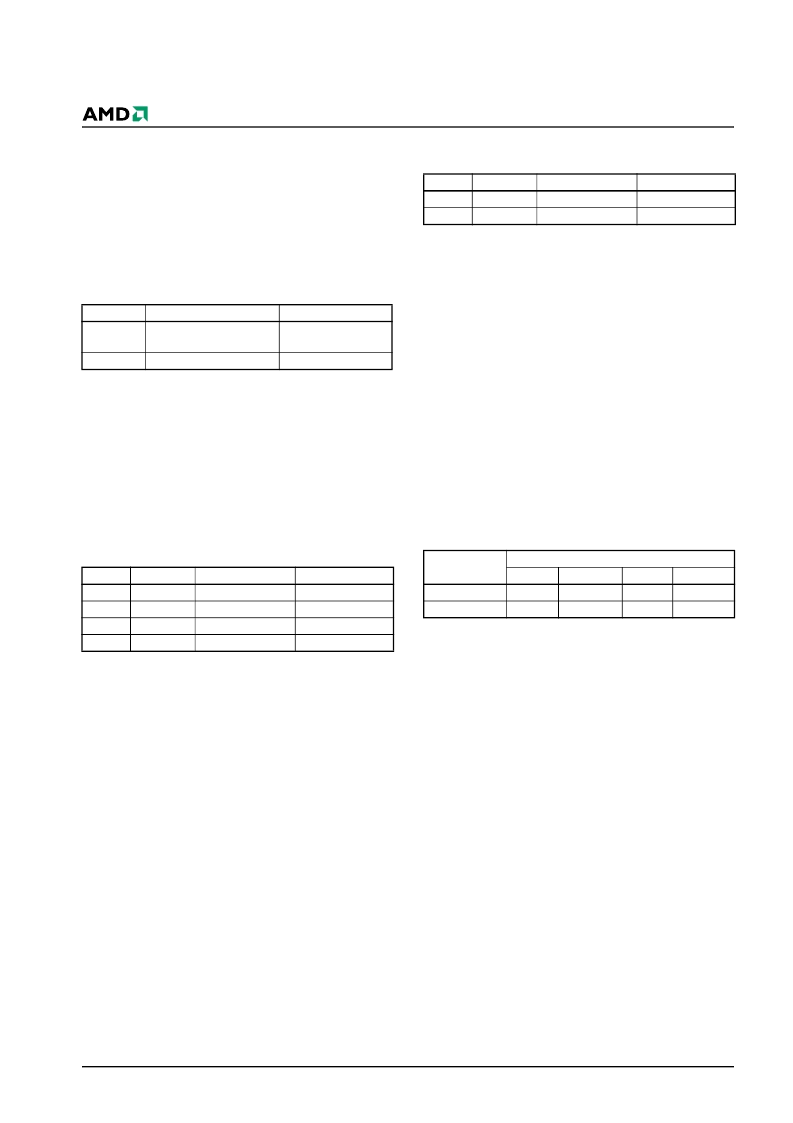

following table for mode features.

The default state is Sleep and it is the lowest power

consumption but all data will be lost once CE2 is

brought to Low for Power Down. It is not required to

program to Sleep mode after power-up.

Power Down Program Sequence

The program requires total 6 read/write operation with

unique address and data. Between each read/write

operation requires that device be in standby mode.

The following table shows the detail sequence.

The first cycle is to read from most significant address

(MSB). The second and third cycle are to write back

the data (RDa) read by first cycle. If the second or third

cycle is written into the different address, the program

is cancelled and the data written by the second or third

cycle is valid as a normal write operation. The fourth

and fifth cycle is to write to MSB. The data of fourth

and fifth cycle is don’t care. If the fourth or fifth cycle is

written into different address, the program is also can-

celled but write data may not be wrote as normal write

operation. The last cycle is to read from specific ad-

dress key for mode selection. Once this program se-

quence is performed from a Partial mode, the write

data may be lost. So, it should perform this program

prior to regular read/write operation if Partial mode is

used.

Address Key

The address key has the following format.

Mode

Sleep

(default)

8M Partial

Data Retention

Retention Address

No

N/A

8M bit

00000h to 7FFFFh

Cycle#

1st

2nd

3rd

4th

Operation

Read

Write

Write

Write

Address

1FFFFFh (MSB)

1FFFFFh

1FFFFFh

1FFFFFh

Data

Read Data (RDa)

RDa

RDa

Don’t Care (X)

5th

6th

Write

Read

1FFFFFh

Address Key

X

Read Data (RDb)

Mode

Address

A19

1

0

A20

1

1

A18-A0

1

1

Binary

1FFFFFh

17FFFFh

Sleep (default)

8M Partial

Cycle#

Operation

Address

Data

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AM49LV128BMH11NS | 128 Megabit (8 M x 16-Bit) MirrorBit⑩ Uniform Sector Flash Memory and 32 Mbit (2 M x 16-Bit) |

| AM49LV128BMH11NT | 128 Megabit (8 M x 16-Bit) MirrorBit⑩ Uniform Sector Flash Memory and 32 Mbit (2 M x 16-Bit) |

| AM49LV128BMH15NS | 128 Megabit (8 M x 16-Bit) MirrorBit⑩ Uniform Sector Flash Memory and 32 Mbit (2 M x 16-Bit) |

| AM49LV128BMH15NT | 128 Megabit (8 M x 16-Bit) MirrorBit⑩ Uniform Sector Flash Memory and 32 Mbit (2 M x 16-Bit) |

| AM49LV128BML11NS | 128 Megabit (8 M x 16-Bit) MirrorBit⑩ Uniform Sector Flash Memory and 32 Mbit (2 M x 16-Bit) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AM49LV128BMH11NS | 制造商:SPANSION 制造商全稱:SPANSION 功能描述:128 Megabit (8 M x 16-Bit) MirrorBit⑩ Uniform Sector Flash Memory and 32 Mbit (2 M x 16-Bit) |

| AM49LV128BMH11NT | 制造商:SPANSION 制造商全稱:SPANSION 功能描述:128 Megabit (8 M x 16-Bit) MirrorBit⑩ Uniform Sector Flash Memory and 32 Mbit (2 M x 16-Bit) |

| AM49LV128BMH15NS | 制造商:SPANSION 制造商全稱:SPANSION 功能描述:128 Megabit (8 M x 16-Bit) MirrorBit⑩ Uniform Sector Flash Memory and 32 Mbit (2 M x 16-Bit) |

| AM49LV128BMH15NT | 制造商:SPANSION 制造商全稱:SPANSION 功能描述:128 Megabit (8 M x 16-Bit) MirrorBit⑩ Uniform Sector Flash Memory and 32 Mbit (2 M x 16-Bit) |

| AM49LV128BML11NS | 制造商:SPANSION 制造商全稱:SPANSION 功能描述:128 Megabit (8 M x 16-Bit) MirrorBit⑩ Uniform Sector Flash Memory and 32 Mbit (2 M x 16-Bit) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。