- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375292 > AM29DL320GT70WDF (SPANSION LLC) For new designs involving TSOP packages, S29JL032H supercedes Am29DL320G and is the factory-recommended migration path. PDF資料下載

參數(shù)資料

| 型號(hào): | AM29DL320GT70WDF |

| 廠商: | SPANSION LLC |

| 元件分類: | DRAM |

| 英文描述: | For new designs involving TSOP packages, S29JL032H supercedes Am29DL320G and is the factory-recommended migration path. |

| 中文描述: | 2M X 16 FLASH 3V PROM, 70 ns, PBGA63 |

| 封裝: | 8 X 14 MM, 0.80 MM PITCH, LEAD FREE, FBGA-63 |

| 文件頁數(shù): | 26/58頁 |

| 文件大?。?/td> | 1239K |

| 代理商: | AM29DL320GT70WDF |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁當(dāng)前第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁

24

Am29DL320G

September 27, 2004

COMMAND DEFINITIONS

Writing specific address and data commands or se-

quences into the command register initiates device op-

erations.

Table 13

defines the valid register command

sequences. Writing

incorrect

address and data val-

ues

or writing them in the

improper sequence

may

place the device in an unknown state. A reset com-

mand is required to return the device to reading array

data.

All addresses are latched on the falling edge of WE#

or CE#, whichever happens later. All data is latched on

the rising edge of WE# or CE#, whichever happens

first. Refer to the AC Characteristics section for timing

diagrams.

Reading Array Data

The device is automatically set to reading array data

after device power-up. No commands are required to

retrieve data. Each bank is ready to read array data

after completing an Embedded Program or Embedded

Erase algorithm.

After the device accepts an Erase Suspend command,

the corresponding bank enters the erase-sus-

pend-read mode, after which the system can read

data from any non-erase-suspended sector within the

same bank. After completing a programming operation

in the Erase Suspend mode, the system may once

again read array data with the same exception. See

the Erase Suspend/Erase Resume Commands sec-

tion for more information.

The system

must

issue the reset command to return a

bank to the read (or erase-suspend-read) mode if DQ5

goes high during an active program or erase opera-

tion, or if the bank is in the autoselect mode. See the

next section, Reset Command, for more information.

See also Requirements for Reading Array Data in the

Device Bus Operations section for more information.

The Read-Only Operations table provides the read pa-

rameters, and

Figure 14

shows the timing diagram.

Reset Command

Writing the reset command resets the banks to the

read or erase-suspend-read mode. Address bits are

don’t cares for this command.

The reset command may be written between the se-

quence cycles in an erase command sequence before

erasing begins. This resets the bank to which the sys-

tem was writing to the read mode. Once erasure be-

gins, however, the device ignores reset commands

until the operation is complete.

The reset command may be written between the

sequence cycles in a program command sequence

before programming begins. This resets the bank to

which the system was writing to the read mode. If the

program command sequence is written to a bank that

is in the Erase Suspend mode, writing the reset

command returns that bank to the erase-sus-

pend-read mode. Once programming begins, however,

the device ignores reset commands until the operation

is complete.

The reset command may be written between the se-

quence cycles in an autoselect command sequence.

Once in the autoselect mode, the reset command

must be written to return to the read mode. If a bank

entered the autoselect mode while in the Erase Sus-

pend mode, writing the reset command returns that

bank to the erase-suspend-read mode.

If DQ5 goes high during a program or erase operation,

writing the reset command returns the banks to the

read mode (or erase-suspend-read mode if that bank

was in Erase Suspend).

Autoselect Command Sequence

The autoselect command sequence allows the host

system to access the manufacturer and device codes,

and determine whether or not a sector is protected.

Table 13

shows the address and data requirements.

This method is an alternative to that shown in

Table 6

,

which is intended for PROM programmers and re-

quires V

ID

on address pin A9. The autoselect com-

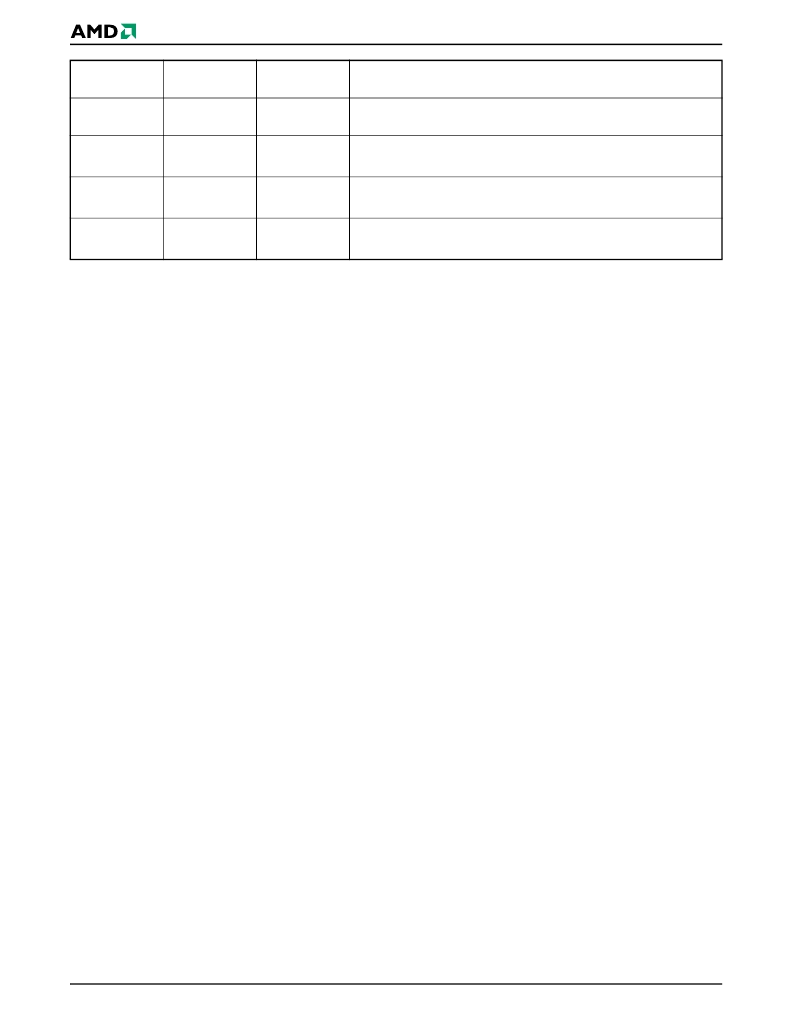

4Ch

98h

0000h

Page Mode Type

00 = Not Supported, 01 = 4 Word Page, 02 = 8 Word Page

4Dh

9Ah

0085h

ACC (Acceleration) Supply Minimum

00h = Not Supported, D7-D4: Volt, D3-D0: 100 mV

4Eh

9Ch

0095h

ACC (Acceleration) Supply Maximum

00h = Not Supported, D7-D4: Volt, D3-D0: 100 mV

4Fh

9Eh

000Xh

Top/Bottom Boot Sector Flag

02h = Bottom Boot Device, 03h = Top Boot Device

Addresses

(Word Mode)

Addresses

(Byte Mode)

Data

Description

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AM29DL320GB70WDF | For new designs involving TSOP packages, S29JL032H supercedes Am29DL320G and is the factory-recommended migration path. |

| AM29DL320GT70WDFN | For new designs involving TSOP packages, S29JL032H supercedes Am29DL320G and is the factory-recommended migration path. |

| AM29DL320GB70WDFN | For new designs involving TSOP packages, S29JL032H supercedes Am29DL320G and is the factory-recommended migration path. |

| AM29DL320GT70WMIN | DIODE SCHOTTKY HEX COMMON-CATHODE 30V 250mW 0.57V-vf 200mA-IFM 30mA-IF 0.7uA-IR DFN1616-6 3K/REEL |

| AM29DL320GB70WMIN | DIODE SCHOTTKY SINGLE 10V 200mW 0.37V-vf 30mA-IFM 1mA-IF 1uA-IR SOT-323 3K/REEL |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AM29DL322DB7REIT | 制造商:AMD 功能描述:New |

| AM29DL322DB-90WDIT | 制造商:Spansion 功能描述:FLASH PARALLEL 3V/3.3V 32MBIT 4MX8/2MX16 90NS 63FBGA - Tape and Reel |

| AM29DL322DT-90EI-T | 制造商:Advanced Micro Devices 功能描述: |

| AM29DL322GB-90EI | 制造商:Advanced Micro Devices 功能描述:2M X 16 FLASH 3V PROM, 90 ns, 48 Pin Plastic SMT |

| AM29DL322GT-90EI | 制造商:Advanced Micro Devices 功能描述:Flash Mem Parallel 3.3V 32M-Bit 4M x 8/2M x 16 90ns 48-Pin TSOP |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。