- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374045 > ADV7152LS135 (ANALOG DEVICES INC) CMOS 220 MHz True-Color Graphics Triple 10-Bit Video RAM-DAC PDF資料下載

參數(shù)資料

| 型號: | ADV7152LS135 |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 顯示控制器 |

| 英文描述: | CMOS 220 MHz True-Color Graphics Triple 10-Bit Video RAM-DAC |

| 中文描述: | PALETTE-DAC DSPL CTLR, PQFP100 |

| 封裝: | PLASTIC, QFP-100 |

| 文件頁數(shù): | 17/32頁 |

| 文件大小: | 454K |

| 代理商: | ADV7152LS135 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁當(dāng)前第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁

ADV7152

–17–

REV. B

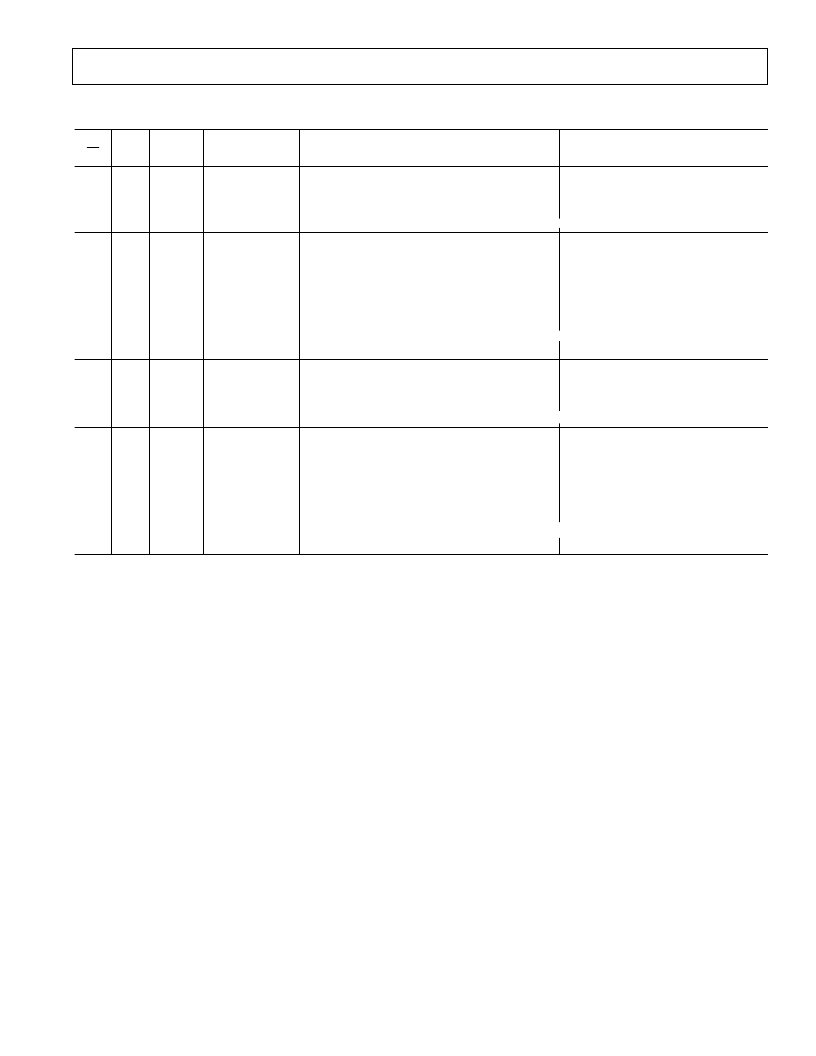

T able IV. Interface T ruth T able (8-Bit Databus Mode)*

Databus

(D9–D0)

R/

W

C1

C0

Operation

Result

0

0

0

1

0

1

1

0

0

DB7–DB0

DB7–DB0

DB7–DB0

Write to Mode Register

Write to Address Register

Write to Control Registers

(

Particular Control Register Determined by Address Register

(

A7–A0

))

DB7–DB0

MR17–MR10

DB7–DB0

A7–A0

DB7–DB0

Control Registers

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

DB9–DB2

DB1–DB0

DB9–DB2

DB1–DB0

DB9–DB2

DB1–DB0

Write to RED Register

Write to RED Register

Write to GREEN Register

Write to GREEN Register

Write to BLUE Register

Write to BLUE Register

Write RGB Data to RAM Location Pointed to by Address Register (A7-A0)

Address Register = Address Register + 1

DB9–DB2

R9–R2

DB1–DB0

R1–R0

DB9–DB2

G9–G2

DB1–DB0

G1–G0

DB9–DB2

B9–B2

DB1–DB0

B1–B0

1

1

1

1

0

1

1

0

0

DB7–DB0

DB7–DB0

DB7–DB0

Read Mode Register

Read Address Register

Read Control Registers

(Particular Control Register Determined by Address Register)

MR17–MR10

DB7–DB0

A7–A0

DB7–DB0

Register Data

DB7–DB0

1

1

1

1

1

1

0

0

0

0

0

0

1

1

1

1

1

1

DB9–DB2

DB1–DB0

DB9–DB2

DB1–DB0

DB9–DB2

DB1–DB0

Read RED RAM Location

Read RED RAM Location

Read GREEN RAM Location

Read GREEN RAM Location

Read BLUE RAM Location

Read BLUE RAM Location

(RAM Location Pointed to by Address Register (A7–A0))

Address Register = Address Register + 1

R9–R2

DB9–DB2

R1–R0

DB1–DB0

G9–G2

DB9–DB2

G1–G0

DB1–DB0

B9–B2

DB9–DB2

B1–B0

DB1–DB0

*Writing or reading 10-bit data (DB9–DB0) over an 8-bit databus (D7–D0) requires two write or two read cycles.

:DB9–DB2 is mapped to D7–D0 on the first cycle.

:DB1–DB0 is mapped to D1–D0 on the second cycle.

DB = Data Bit.

Power-On Reset

On power-up of the ADV7152 executes a power-on reset opera-

tion. T his initializes the pixel port such that the pixel sequence

AB starts at A. T he Mode Register (MR17–MR10), Command

Register 2 (CR27–CR20) and Command Register 3 (CR37–

CR30) have all bits set to a Logic “1.” Command Register 1

(CR17–CR10) has all bits set to a Logic “0.”

T he output clocking signals are also set during this reset period.

PRGCK OUT = CLOCK /32

LOADOUT = CLOCK /2

T he power-on reset is activated when V

AA

goes from 0 V to

5 V. T his reset is active for 1

μ

s. T he ADV7152 should not be

accessed during this reset period. T he pixel clock should be

applied at power-up.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADV7152LS170 | CMOS 220 MHz True-Color Graphics Triple 10-Bit Video RAM-DAC |

| ADV7152LS220 | CMOS 220 MHz True-Color Graphics Triple 10-Bit Video RAM-DAC |

| ADV7160 | 96-Bit, 220 MHz True-Color Video RAM-DAC(96位,220MHz,真彩色視頻RAM-D/A轉(zhuǎn)換器) |

| ADV7162 | 96-Bit, 220 MHz True-Color Video RAM-DAC(96位,220MHz,真彩色視頻RAM-D/A轉(zhuǎn)換器) |

| ADV7162KS140 | 96-Bit, 220 MHz True-Color Video RAM-DAC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADV7152LS170 | 制造商:AD 制造商全稱:Analog Devices 功能描述:CMOS 220 MHz True-Color Graphics Triple 10-Bit Video RAM-DAC |

| ADV7152LS220 | 制造商:Analog Devices 功能描述: 制造商:Analog Devices 功能描述:PALETTE-DAC DSPL CTLR, PQFP100 |

| ADV7152LS85 | 制造商:AD 制造商全稱:Analog Devices 功能描述:CMOS 220 MHz True-Color Graphics Triple 10-Bit Video RAM-DAC |

| ADV7160 | 制造商:AD 制造商全稱:Analog Devices 功能描述:96-Bit, 220 MHz True-Color Video RAM-DAC |

| ADV7160KS140 | 制造商:Analog Devices 功能描述: 制造商:Rochester Electronics LLC 功能描述:220 MHZ VIDEO RAM DAC I.C. - Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。