- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374025 > ADR292GR-REEL (ANALOG DEVICES INC) Low Noise Micropower Precision Voltage References PDF資料下載

參數(shù)資料

| 型號: | ADR292GR-REEL |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 基準電壓源/電流源 |

| 英文描述: | Low Noise Micropower Precision Voltage References |

| 中文描述: | 1-OUTPUT THREE TERM VOLTAGE REFERENCE, 4.096 V, PDSO8 |

| 封裝: | MS-012AA, SOIC-8 |

| 文件頁數(shù): | 12/15頁 |

| 文件大小: | 199K |

| 代理商: | ADR292GR-REEL |

REV. B

ADR290/ADR291/ADR292

–12–

Device Power Dissipation Considerations

The ADR29x family of references is guaranteed to deliver load

currents to 5 mA with an input voltage that ranges from 2.7 V

to 15 V (minimum supply voltage depends on output voltage

option). When these devices are used in applications with large

input voltages, care should be exercised to avoid exceeding the

published specifications for maximum power dissipation or junc-

tion temperature that could result in premature device failure.

The following formula should be used to calculate a device

’

s maxi-

mum junction temperature or dissipation:

P

T

T

D

A

A

=

J

J

–

θ

In this equation,

T

J

and

T

A

are the junction and ambient tem-

peratures, respectively,

P

D

is the device power dissipation, and

θ

J

A

is the device package thermal resistance.

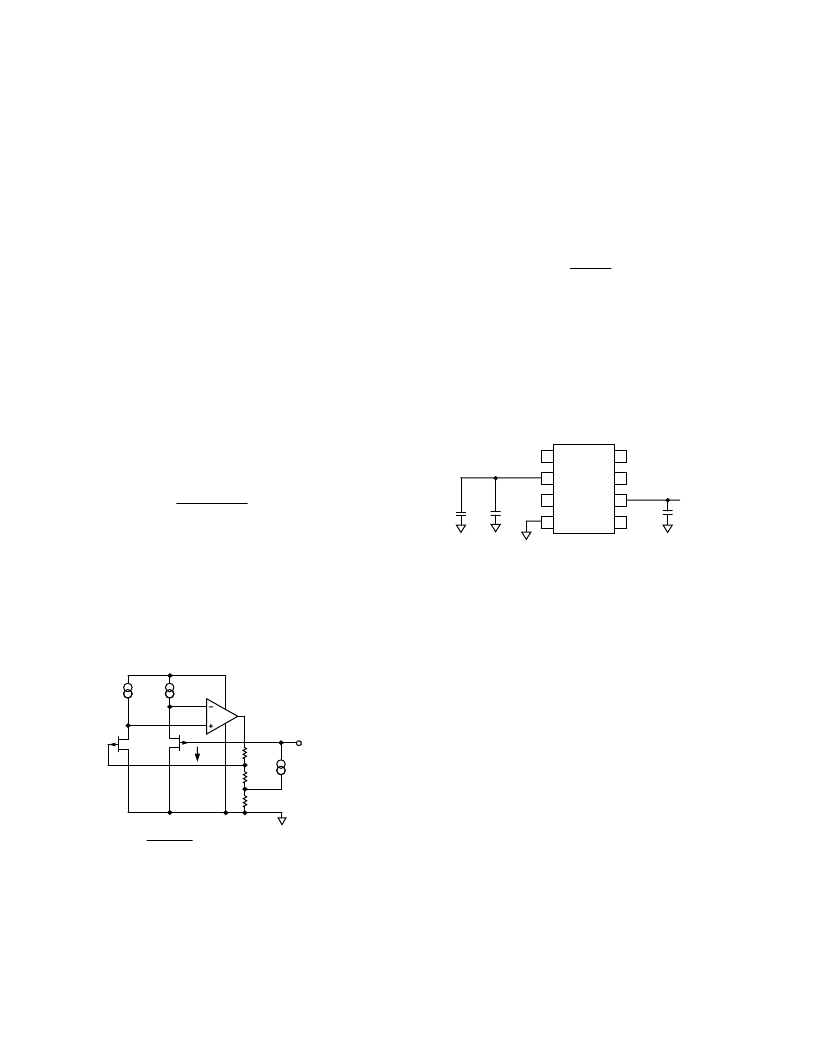

Basic Voltage Reference Connections

References, in general, require a bypass capacitor connected

from the V

OUT

pin to the GND pin. The circuit in Figure 2

illustrates the basic configuration for the ADR29x family of ref-

erences. Note that the decoupling capacitors are not required for

circuit stability.

ADR29x

1

2

3

4

8

7

6

5

NC

NC

NC

NC

OUTPUT

NC

0.1 F

0.1 F

10 F

+

NC = NO CONNECT

Figure 2. Basic Voltage Reference Configuration

Noise Performance

The noise generated by the ADR29x family of references is typi-

cally less than 12

μ

V p-p over the 0.1 Hz to 10 Hz band. TPC

21 shows the 0.1 Hz to 10 Hz noise of the ADR290 which is only

6

μ

V p-p. The noise measurement is made with a bandpass filter

made of a 2-pole high-pass filter with a corner frequency at 0.1 Hz

and a 2-pole low-pass filter with a corner frequency at 10 Hz.

Turn-On Time

Upon application of power (cold start), the time required for the

output voltage to reach its final value within a specified error band

is defined as the turn-on settling time. Two components nor-

mally associated with this are the time for the active circuits to

settle, and the time for the thermal gradients on the chip to sta-

bilize. TPC 28 shows the turn-on settling time for the ADR291.

THEORY OF OPERATION

The ADR29x series of references uses a new reference generation

technique known as XFET (eXtra implanted junction FET). This

technique yields a reference with low noise, low supply current

and very low thermal hysteresis.

The core of the XFET reference consists of two junction field-

effect transistors, one of which has an extra channel implant to

raise its pinch-off voltage. By running the two JFETs at the

same drain current, the difference in pinch-off voltage can be

amplified and used to form a highly stable voltage reference.

The intrinsic reference voltage is around 0.5 V with a negative

temperature coefficient of about

–

120 ppm/K. This slope is

essentially locked to the dielectric constant of silicon and can be

closely compensated by adding a correction term generated in

the same fashion as the proportional-to-temperature (PTAT)

term used to compensate bandgap references. The big advantage

over a bandgap reference is that the intrinsic temperature coeffi-

cient is some thirty times lower (therefore less correction is

needed) and this results in much lower noise since most of the

noise of a bandgap reference comes from the temperature com-

pensation circuitry.

The simplified schematic below shows the basic topology of the

ADR29x series. The temperature correction term is provided by

a current source with value designed to be proportional to abso-

lute temperature. The general equation is:

V

V

R

R

R

R

I

R

OUT

P

PTAT

=

+

+

+

(

)(

)

1

2

1

3

3

where

V

P

is the difference in pinch-off voltage between the two

FETs, and

I

PTAT

is the positive temperature coefficient correc-

tion current. The various versions of the ADR29x family are

created by on-chip adjustment of R1 and R3 to achieve 2.048 V,

2.500 V or 4.096 V at the reference output.

The process used for the XFET reference also features vertical

NPN and PNP transistors, the latter of which are used as output

devices to provide a very low drop-out voltage.

V

OUT

V

IN

I

PTAT

GND

R1

R2

R3

I

1

I

1

*

*

EXTRA

CHANNEL

IMPLANT

V

OUT

=R1

+

R2

+

R3

R1

V

P

+ I

PTAT

R3

V

P

Figure 1. ADR290/ADR291/ADR292 Simplified Schematic

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADR292GR-REEL7 | Low Noise Micropower Precision Voltage References |

| ADR290GRU-REEL | Low Noise Micropower Precision Voltage References |

| ADR291GRU-REEL | Low Noise Micropower Precision Voltage References |

| ADR292GRU-REEL | Low Noise Micropower Precision Voltage References |

| ADR290GT9-REEL | Low Noise Micropower Precision Voltage References |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADR292GR-REEL7 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Low Noise Micropower Precision Voltage References |

| ADR292GR-RELL | 制造商:AD 制造商全稱:Analog Devices 功能描述:Low Noise Micropower Precision Voltage References |

| ADR292GRU | 制造商:Analog Devices 功能描述:V-Ref Precision 4.096V 5mA 8-Pin TSSOP Tube |

| ADR292GRU-REEL | 制造商:AD 制造商全稱:Analog Devices 功能描述:Low Noise Micropower Precision Voltage References |

| ADR292GRU-REEL7 | 制造商:Analog Devices 功能描述:V-Ref Precision 4.096V 5mA 8-Pin TSSOP T/R 制造商:Rochester Electronics LLC 功能描述:- Tape and Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復。