- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373996 > ADM1064ACP (ANALOG DEVICES INC) Super Sequencer with Voltage Readback ADC PDF資料下載

參數(shù)資料

| 型號: | ADM1064ACP |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 電源管理 |

| 英文描述: | Super Sequencer with Voltage Readback ADC |

| 中文描述: | 10-CHANNEL POWER SUPPLY SUPPORT CKT, QCC40 |

| 封裝: | 6 X 6 MM, MO-220-VJJD-2, LFCS-40 |

| 文件頁數(shù): | 14/32頁 |

| 文件大?。?/td> | 523K |

| 代理商: | ADM1064ACP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁當(dāng)前第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁

ADM1064

INPUT COMPARATOR HYSTERESIS

The UV and OV comparators shown in Figure 19 are always

looking at VPn. To avoid chattering (multiple transitions when

the input is very close to the set threshold level), these compara-

tors have digitally programmable hysteresis. The hysteresis can

be programmed up to the values shown in Table 5.

Rev. 0 | Page 14 of 32

The hysteresis is added after a supply voltage goes out of

tolerance. Therefore, the user can program how much above the

UV threshold the input must rise again before a UV fault is

deasserted. Similarly, the user can program how much below the

OV threshold an input must fall again before an OV fault is

deasserted.

The hysteresis figure is given by

V

HYST

=

V

R

×

N

THRESH

/255

where:

V

HYST

is the desired hysteresis voltage.

N

THRESH

is the decimal value of the 5-bit hysteresis code.

Note that

N

THRESH

has a maximum value of 31. The maximum

hysteresis for the ranges is listed in Table 5.

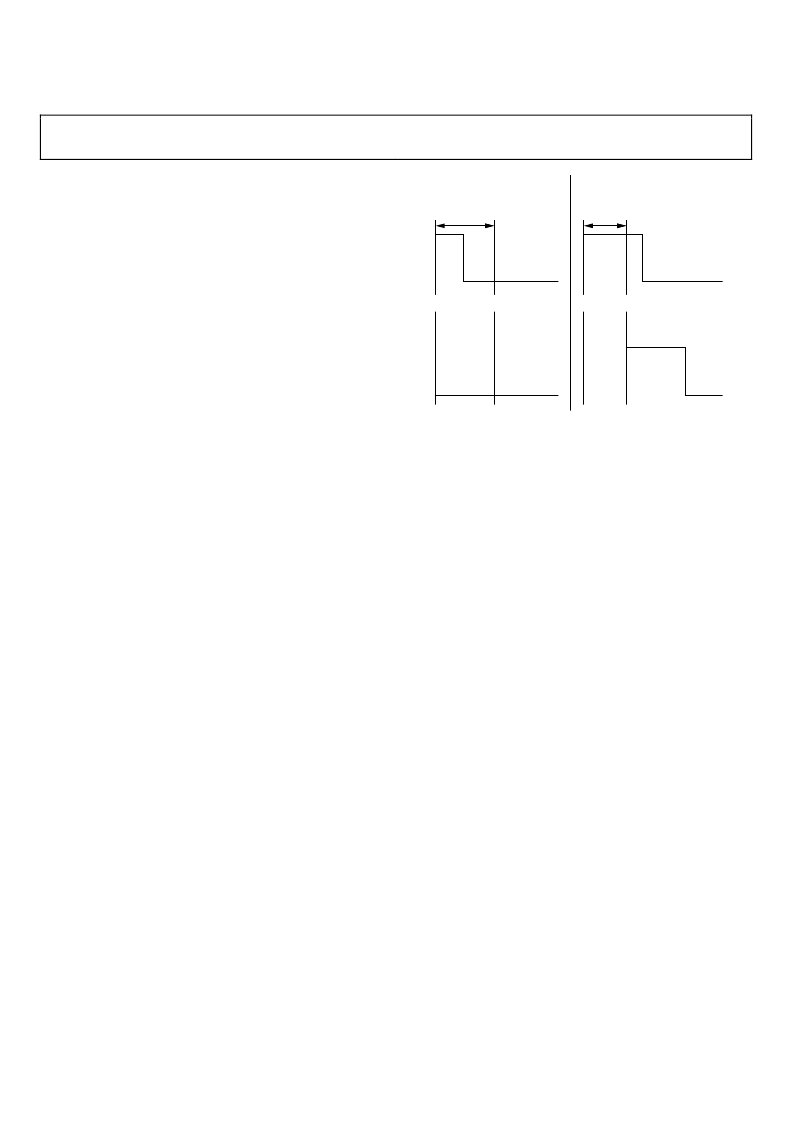

INPUT GLITCH FILTERING

The final stage of the SFDs is a glitch filter. This block provides

time-domain filtering on the output of the SFD comparators.

This allows the user to remove any spurious transitions such as

supply bounce at turn-on. The glitch filter function is additional

to the digitally programmable hysteresis of the SFD compara-

tors. The glitch filter timeout is programmable up to 100 μs.

For example, when the glitch filter timeout is 100 μs, any pulses

appearing on the input of the glitch filter block that are less than

100 μs in duration are prevented from appearing on the output

of the glitch filter block. Any input pulse that is longer than

100 μs does appear on the output of the glitch filter block. The

output is delayed with respect to the input by 100 μs. The

filtering process is shown in Figure 20.

0

T

0

T

GF

T

0

T

GF

T

0

T

GF

T

0

T

GF

INPUT

INPUT PULSE SHORTER

THAN GLITCH FILTER TIMEOUT

INPUT PULSE LONGER

THAN GLITCH FILTER TIMEOUT

OUTPUT

PROGRAMMED

TIMEOUT

PROGRAMMED

TIMEOUT

INPUT

OUTPUT

Figure 20. Input Glitch Filter Function

SUPPLY SUPERVISION WITH VXn INPUTS

The VXn inputs have two functions. They can be used as either

supply fault detectors or digital logic inputs. When selected as

an analog (SFD) input, the VXn pins have very similar func-

tionality to the VH and VPn pins. The major difference is that

the VXn pins have only one input range: 0.573 V to 1.375 V.

Therefore, these inputs can directly supervise only the very low

supplies. However, the input impedance of the VXn pins is high,

allowing an external resistor divide network to be connected to

the pin. Thus, any supply can be potentially divided down into

the input range of the VXn pin and supervised. This enables the

ADM1064 to monitor other supplies such as +24 V, +48 V, and

5 V.

An additional supply supervision function is available when the

VXn pins are selected as digital inputs. In this case, the analog

function is available as a second detector on each of the dedi-

cated analog inputs, VP1–4 and VH. The analog function of

VX1 is mapped to VP1, VX2 is mapped to VP2, and so on. VX5

is mapped to VH. In this case, these SFDs can be viewed as a

secondary or warning SFD.

The secondary SFDs are fixed to the same input range as the

primary SFD. They are used to indicate warning levels rather

than failure levels. This allows faults and warnings to be gener-

ated on a single supply using only one pin. For example, if VP1

is set to output a fault if a 3.3 V supply droops to 3.0 V, VX1 can

be set to output a warning at 3.1 V. Warning outputs are available

for readback from the status registers. They are also OR’ed

together and fed into the sequencing engine (SE), allowing

warnings to generate interrupts on the PDOs. Therefore, in the

example above, if the supply droops to 3.1 V, a warning is

generated, and remedial action can be taken before the supply

drops out of tolerance.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADM1064ACP-REEL | Super Sequencer with Voltage Readback ADC |

| ADM1064ACP-REEL7 | Super Sequencer with Voltage Readback ADC |

| ADM1064ASU | Super Sequencer with Voltage Readback ADC |

| ADM1064ASU-REEL | Super Sequencer with Voltage Readback ADC |

| ADM1064ASU-REEL7 | Super Sequencer with Voltage Readback ADC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADM1064ACP-REEL | 制造商:Analog Devices 功能描述:Volt Supervisor Sequencer 2.7V to 5.4V 40-Pin LFCSP EP T/R |

| ADM1064ACP-REEL7 | 制造商:Analog Devices 功能描述:Volt Supervisor Sequencer 2.7V to 5.4V 40-Pin LFCSP EP T/R |

| ADM1064ACPZ | 功能描述:IC SEQUENCER/SUPERVISOR 40-LFCSP RoHS:是 類別:集成電路 (IC) >> PMIC - 監(jiān)控器 系列:Super Sequencer® 標(biāo)準(zhǔn)包裝:1 系列:- 類型:簡單復(fù)位/加電復(fù)位 監(jiān)視電壓數(shù)目:1 輸出:開路漏極或開路集電極 復(fù)位:高有效 復(fù)位超時:- 電壓 - 閥值:1.8V 工作溫度:-40°C ~ 125°C 安裝類型:表面貼裝 封裝/外殼:6-TSOP(0.059",1.50mm 寬)5 引線 供應(yīng)商設(shè)備封裝:5-TSOP 包裝:剪切帶 (CT) 其它名稱:NCP301HSN18T1GOSCT |

| ADM1064ASU | 制造商:Analog Devices 功能描述:Volt Supervisor Sequencer 2.7V to 5.4V 48-Pin TQFP |

| ADM1064ASU-REEL | 制造商:Analog Devices 功能描述:Volt Supervisor Sequencer 2.7V to 5.4V 48-Pin TQFP T/R |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。