- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373980 > ADE7756EB (Analog Devices, Inc.) Evaluation Board Documentation AD7756 Energy metering IC PDF資料下載

參數(shù)資料

| 型號: | ADE7756EB |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | Evaluation Board Documentation AD7756 Energy metering IC |

| 中文描述: | 評估板文檔AD7756電能計量IC |

| 文件頁數(shù): | 4/15頁 |

| 文件大小: | 3563K |

| 代理商: | ADE7756EB |

EVAL-ADE7756EB

–4–

REV. PrB 01/01

PRELIMINARY TECHNICAL DATA

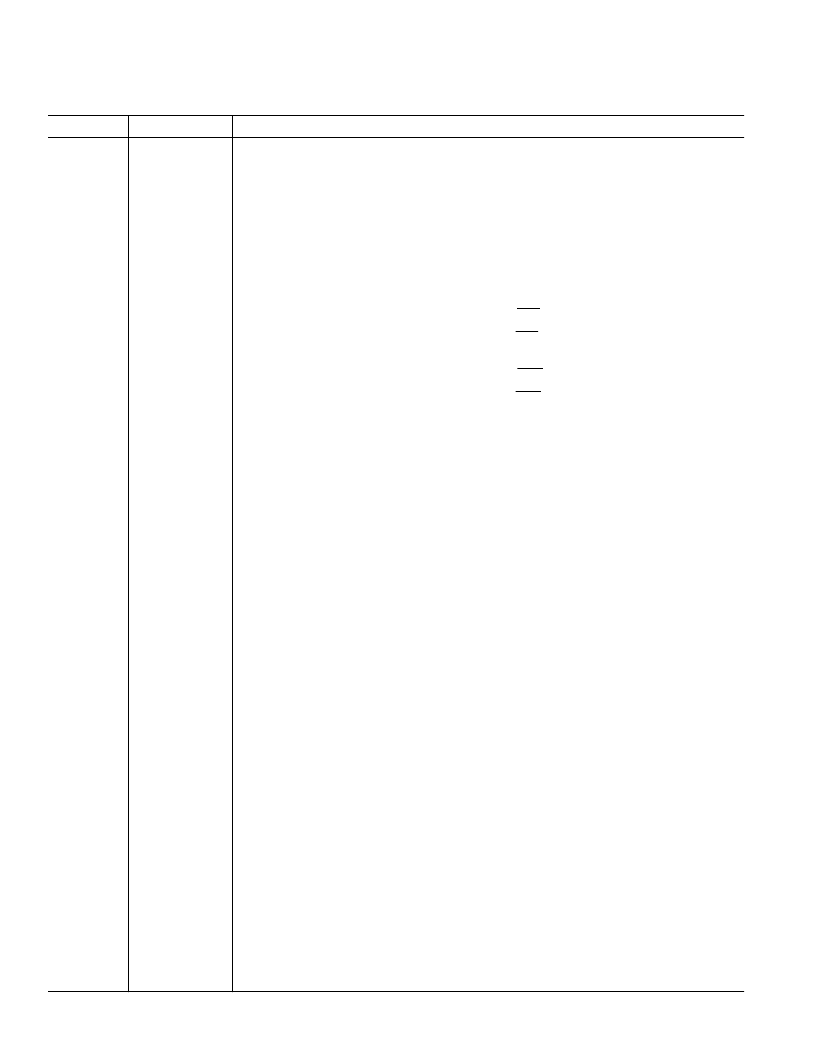

JUMEPER

OPTION

DESCRIPTION

JP1

Closed

This will short out R50. The effect is to disable the anti-alias filter on the

analog input V1P. Default Open.

Open

Enable the anti-alias filter on V1P.

JP2

Closed

This will connect the analog input V1P to ground. Default Open.

JP3

Closed

This will short out R51. The effect is to disable the anti-alias filter on the

analog input V1N. Default Open.

Open

Enabe the anti-alias filter on V1N.

JP4

Closed

This will connect the analog input V1N to ground. Default Open.

JP5

A

This connects the buffered logic output

IRQ

to the LED1.

B

This connects the buffered logic output

IRQ

to pin 10 on the D-Sub connector

via an optical isolator.

JP6

A

This connects the buffered logic output

SAG

to the LED2.

B

This connects the buffered logic output

SAG

to pin 11 on the D-Sub connector

via an optical isolator.

JP7

Closed

This will short the attenuation network on Channel 2. Default open.

JP8

Closed

This will connect the analog input V2P to ground. Default Open.

JP9

Closed

This will short out R57. The effect is to disable the anti-alias filter on the

analog input V2N. Default Open.

Open

Enable the anti-alias filter on V2N.

JP10

Closed

This will connect the analog input V2N to ground. Default Open.

JP11

Closed

This will connect the Analog and Digital ground planes of the PCB. Default

Closed.

JP12

A

This connects the buffered logic output CF to the LED4.

B

This connects the buffered logic output CF to BNC2 connector via an optical

isolator.

JP13

Closed

This will connect an external reference 2.5V (AD780) to the ADE7756.

Open

This will enable the ADE7756 on-chip reference.

JP14

Closed

This will connect the optical isolator ground to the evaluation board gound

(DGND). If full isolation between the evaluation board and PC is required,

this jumper should be left open.

JP15

Closed

This will short out R41. The effect is to disable the phase compensation filter

(for shunts) on the analog input V1P. Default Closed.

JP19

A

This connects the buffered logic output ZX to the LED3.

B

This connects the buffered logic output ZX to pin 12 on the D-Sub connector

via an optical isolator.

JP20

Closed

This connects the AVDD and DVDD supply for the evaluation board together.

Default Closed.

JP21

Closed

This connects the DVDD and +5V (buffers) supply for the evaluation board

together. Default Closed.

JP25

Closed

This will short out R42. The effect is to disable the phase compensation filter

(for shunts) on the analog input V1N. Default Closed.

JP51

Closed

This will short out disconnect Analog input V2P from the ADE7756. Default

Closed.

JUMPER SETTINGS

相關PDF資料 |

PDF描述 |

|---|---|

| ADE7756 | Active Energy Metering IC with Serial Interface |

| ADE7756AN | Active Energy Metering IC with Serial Interface |

| ADE7756AN-REF | Active Energy Metering IC with Serial Interface |

| ADE7756ARS | Active Energy Metering IC with Serial Interface |

| ADE7756ARSRL | Active Energy Metering IC with Serial Interface |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| ADE7757 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Energy Metering IC with Integrated Oscillator |

| ADE7757ARN | 制造商:Rochester Electronics LLC 功能描述:ENERGY METER IC W/INTEGRATED OSCILLATOR - Bulk 制造商:Analog Devices 功能描述:IC ENERGY METER |

| ADE7757ARN-REF | 制造商:Analog Devices 功能描述:REF BOARD ENERGY MTR W/INTGRATED OSCIL. - Rail/Tube |

| ADE7757ARNRL | 制造商:Analog Devices 功能描述:IC ENERGY METERING 16-SOIC TR |

| ADE7757ARNZ | 功能描述:IC ENERGY METERING 1PHASE 16SOIC RoHS:是 類別:集成電路 (IC) >> PMIC - 能量測量 系列:- 產(chǎn)品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:2,500 系列:* |

發(fā)布緊急采購,3分鐘左右您將得到回復。