- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384090 > ADC1215S065HN (NXP Semiconductors N.V.) Single 12-bit ADC 65 Msps with Input Buffer CMOS or LVDS DDR digital outputs PDF資料下載

參數(shù)資料

| 型號: | ADC1215S065HN |

| 廠商: | NXP Semiconductors N.V. |

| 元件分類: | 外設(shè)及接口 |

| 英文描述: | Single 12-bit ADC 65 Msps with Input Buffer CMOS or LVDS DDR digital outputs |

| 封裝: | ADC1215S065HN/C1<SOT618-6 (HVQFN40)|<<http://www.nxp.com/packages/SOT618-6.html<1<Always Pb-free,;ADC1215S065HN/C1<SOT618-6 (HVQFN40)|<<http://www.nxp.com/packages/SOT618 |

| 文件頁數(shù): | 17/42頁 |

| 文件大小: | 292K |

| 代理商: | ADC1215S065HN |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁當(dāng)前第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁

ADC1215S_SER

All information provided in this document is subject to legal disclaimers.

NXP B.V. 2011. All rights reserved.

Product data sheet

Rev. 2 — 13 January 2011

17 of 42

NXP Semiconductors

ADC1215S series

Single 12-bit ADC; input buffer; CMOS or LVDS DDR digital output

11. Application information

11.1 Device control

The ADC1215S can be controlled via the Serial Peripheral Interface (SPI control mode) or

directly via the I/O pins (Pin control mode).

11.1.1

SPI and Pin control modes

The device enters Pin control mode at power-up, and remains in this mode as long as pin

CS is held HIGH. In Pin control mode, the SPI pins SDIO, CS and SCLK are used as

static control pins.

SPI control mode is enabled by forcing pin CS LOW. Once SPI control mode has been

enabled, the device remains in this mode. The transition from Pin control mode to SPI

control mode is illustrated in

Figure 13

.

When the device enters SPI control mode, the output data standard and data format are

determined by the level on pin SDIO as soon as a transition is triggered by a falling edge

on CS.

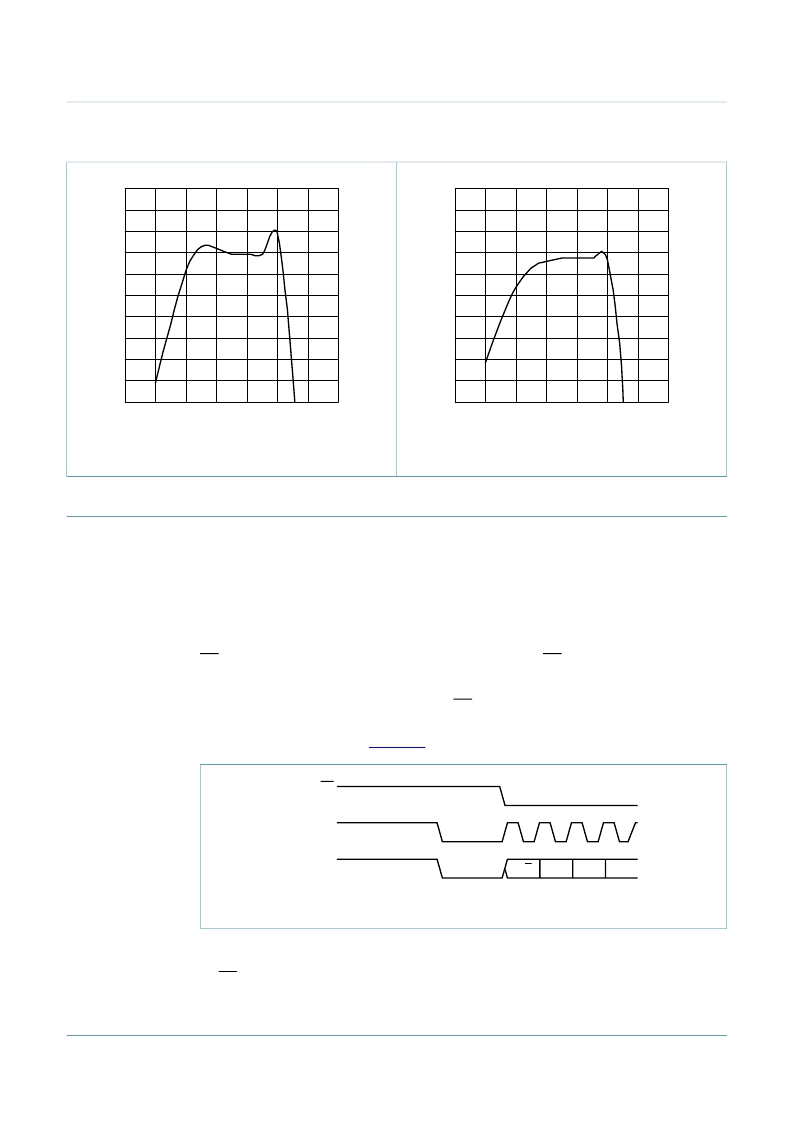

Fig 11. Spurious-free dynamic range as a function of

common-mode input voltage (V

i(cm)

)

Fig 12. Signal-to-noise ratio as a function of

common-mode input voltage (V

i(cm)

)

V

I(cm)

(V)

3.5

2.5

0.5

3.0

2.0

1.0

0

1.5

001aam659

78

74

86

82

90

SFDR

(dBc)

70

V

I(cm)

(V)

3.5

2.5

0.5

3.0

2.0

1.0

0

1.5

001aam660

69

67

73

71

75

SNR

(dBFS)

65

Fig 13. Control mode selection

R/W

SPI control mode

Pin control mode

Data format

offset binary

Data format

two's complement

LVDS DDR

SDIO/ODS

SCLK/DFS

W1

W0

A12

005aaa039

CMOS

CS

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADC1215S080HN | Single 12-bit ADC 80 Msps with Input Buffer CMOS or LVDS DDR digital outputs |

| ADC1215S105HN | Single 12-bit ADC 105 Msps with Input Buffer CMOS or LVDS DDR digital outputs |

| ADC1215S125HN | Single 12-bit ADC 125 Msps with Input Buffer CMOS or LVDS DDR digital outputs |

| ADC1415S065F1 | |

| ADC1415S065HN | Single 14-bit ADC 65 Msps with Input Buffer CMOS or LVDS DDR digital outputs |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADC1215S065HN/C1 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Single 12-bit ADC; 65 Msps, 80 Msps, 105 Msps or 125 Msps with input buffer; CMOS or LVDS DDR digital outputs |

| ADC1215S065HN/C1,5 | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC SGL 12BIT ADC 65MSPS IN BUF CMOS/LVDS DDR RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| ADC1215S065HN-C1 | 制造商:Integrated Device Technology Inc 功能描述:HVQFN40 - Bulk |

| ADC1215S065HN-C18 | 制造商:Integrated Device Technology Inc 功能描述:HVQFN40 - Tape and Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。