- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄97841 > AD8346ARUZ-REEL7 (ANALOG DEVICES INC) 800 MHz - 2500 MHz RF/MICROWAVE I/Q MODULATOR PDF資料下載

參數(shù)資料

| 型號: | AD8346ARUZ-REEL7 |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 調(diào)制器/解調(diào)器 |

| 英文描述: | 800 MHz - 2500 MHz RF/MICROWAVE I/Q MODULATOR |

| 封裝: | LEAD FREE, TSSOP-16 |

| 文件頁數(shù): | 4/20頁 |

| 文件大?。?/td> | 397K |

| 代理商: | AD8346ARUZ-REEL7 |

AD8346

Rev. A | Page 12 of 20

INTERFACE TO AD9761 TXDAC

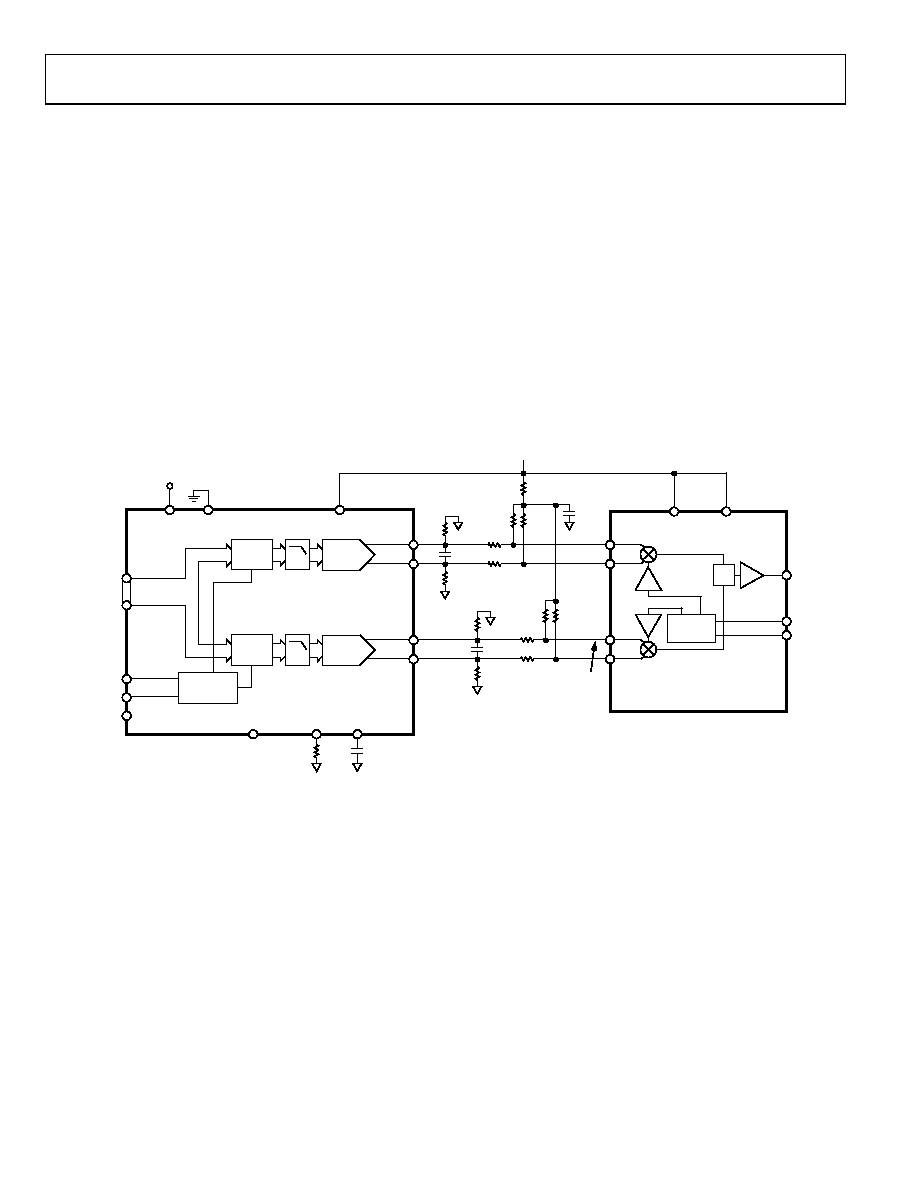

Figure 28 shows a dc-coupled current output DAC interface.

The use of dual-integrated DACs, such as the AD9761 with

specified ±0.02 dB and ±0.004 dB gain and offset matching

characteristics, ensures minimum error contribution (over

temperature) from this portion of the signal chain. The use of a

precision thin-film resistor network sets the bias levels precisely

to prevent the introduction of offset errors, which increase LO

feedthrough. For instance, selecting resistor networks with a

0.1% ratio matching characteristics maintains 0.03 dB gain and

offset matching performance.

Using resistive division, the dc bias level at the I and Q inputs

to the AD8346 is set to approximately 1.2 V. Each of the four

current outputs of the DAC delivers a full-scale current of

10 mA, giving a voltage swing of 0 V to 1 V (at the DAC

output). This results in a 0.5 V p-p swing at the I and Q inputs

of the AD8346 (resulting in a 1 V p-p differential swing).

Note that the ratio matching characteristics of the resistive

network, as opposed to its absolute accuracy, is critical in

preserving the gain and offset balance between the I and Q

signal path.

By applying small dc offsets to the I and Q signals from the

DAC, the LO suppression can be reduced from its nominal

value of 42 dBm to as low as 60 dBm while holding to

approximately 50 dBm over temperature (see Figure 12 for

a plot of LO feedthrough over temperature for an offset

compensated circuit).

I

DAC

2

×

LATCH

I

IOUTB

IOUTA

Q

DAC

2

×

LATCH

Q

QOUTB

QOUTA

MUX

CONTROL

SELECT

WRITE

CLOCK

AD9761

DVDD

DCOM

AVDD

0.1

μF

RSET

2k

Ω

SLEEP

FS ADJ

REFIO

DAC

DATA

INPUTS

CFILTER

100

Ω

100

Ω

CFILTER

100

Ω

100

Ω

500

Ω

500

Ω

500

Ω

500

Ω

500

Ω

500

Ω

500

Ω

500

Ω

0.1

μF

634

Ω

5V

PHASE

SPLITTER

Σ

VOUT

IBBP

IBBN

QBBP

QBBN

AD8346

LOIP

LOIN

VPS1

VPS2

0.5V p-p EACH PIN

WITH VCM = 1.2V

+5V

05335-028

Figure 28. AD8346 Interface to AD9761 TxDAC

相關PDF資料 |

PDF描述 |

|---|---|

| AD8347ARUZ | 800 MHz - 2700 MHz RF/MICROWAVE QUADRAPHASE DEMODULATOR |

| AD8347ARUZ-REEL7 | 800 MHz - 2700 MHz RF/MICROWAVE QUADRAPHASE DEMODULATOR |

| AD8349AREZ-RL7 | 700 MHz - 2700 MHz RF/MICROWAVE QPSK MODULATOR |

| AD8349AREZ-REEL7 | 700 MHz - 2700 MHz RF/MICROWAVE QPSK MODULATOR |

| AD8350ARMZ20 | 1000 MHz RF/MICROWAVE WIDE BAND MEDIUM POWER AMPLIFIER |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| AD8346ARUZ-REEL71 | 制造商:AD 制造商全稱:Analog Devices 功能描述:0.8 GHz to 2.5 GHz Quadrature Modulator |

| AD8346ARUZ-RL7 | 制造商:Analog Devices 功能描述:QUADRATURE MOD 70MHZ 16TSSOP - Tape and Reel |

| AD8346EVAL | 制造商:AD 制造商全稱:Analog Devices 功能描述:0.8 GHz to 2.5 GHz Quadrature Modulator |

| AD8346-EVAL | 制造商:Analog Devices 功能描述:AD8346 EVALUATION BOARD - Bulk |

| AD8346-EVALZ | 制造商:Analog Devices 功能描述:- Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復。