- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375238 > AD7751 (Analog Devices, Inc.) Energy Metering IC with On-Chip Fault Detection(高精度容錯(cuò)電子能量測量芯片) PDF資料下載

參數(shù)資料

| 型號: | AD7751 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | Energy Metering IC with On-Chip Fault Detection(高精度容錯(cuò)電子能量測量芯片) |

| 中文描述: | 電能計(jì)量IC片故障檢測(高精度容錯(cuò)電子能量測量芯片) |

| 文件頁數(shù): | 12/16頁 |

| 文件大小: | 287K |

| 代理商: | AD7751 |

AD7751

12

PRELIM B1 1098

AD7751 TRANSFER FUNCTION

Frequency Outputs F1 and F2

The AD7751 calculates the product of two voltage signals (on

Channel 1 and Channel 2) and then low pass filters this

product to extract real power information. This real power

information is then converted to a frequency. The frequency

information is output on F1 and F2 in the form of active low

pulses. The pulse rate at these outputs is relatively low, e.g.

0.17Hz maximun for ac signals with S0 = S1 = 0

—see Table III. This means that the frequency at these outputs

is generated from real power information accumulated over a

relatively long period of time. The result is an output frequency

which is proportional to the averge real power. The averaging

of the real power signal is implicit to the digital to frequency

conversion. The output frequency or pulse rate is related to the

input voltage signals by the following equation.

Freq

5.7

V1 V2 Gain

V

REF

F

1 - 4

2

=

×

×

where,

Freq

V1

=

=

Output frequency on F1 and F2 (Hz)

Differential RMS voltage signal on Channel 1

(volts)

Differential RMS voltage signal on Channel 2

(volts)

1, 2, 8 or 16 depending on the PGA gain selection

made using logic inputs G0 and G1

The reference voltage (2.5V ± 8%) (volts)

One of four possible frequencies selected by using

the logic inputs S0 and S1—see Table II

V2

=

Gain

=

V

REF

F

1-4

=

=

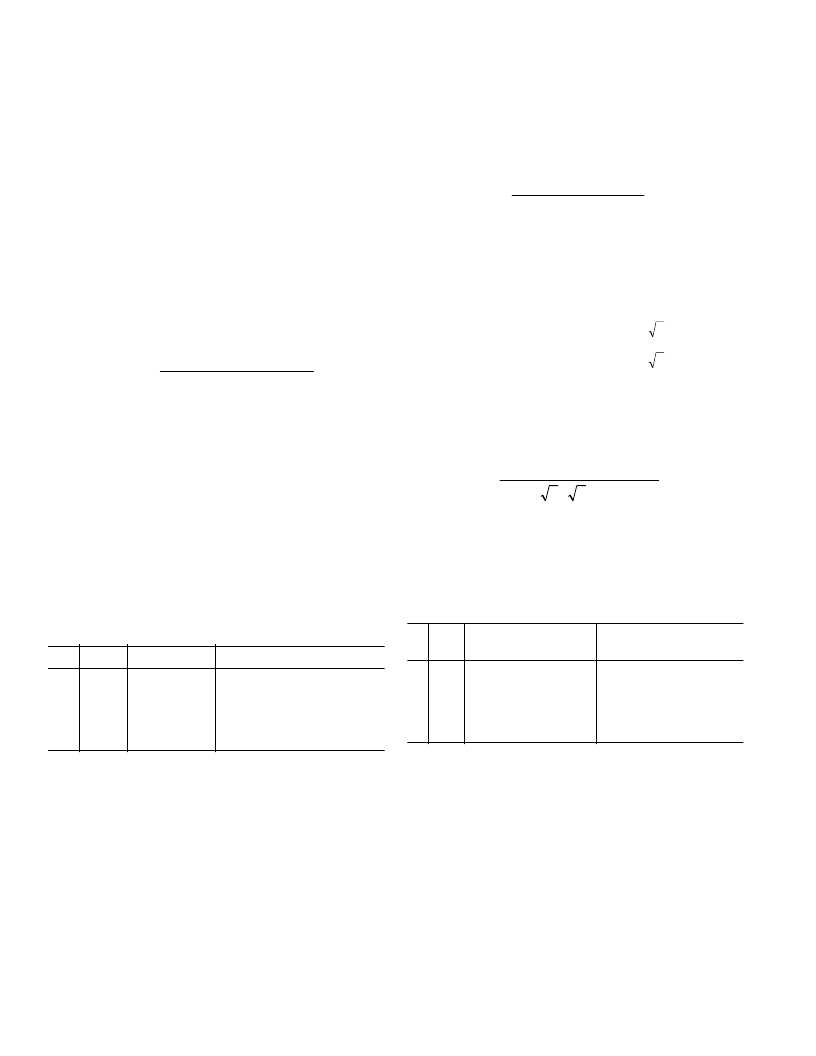

TABLE II

S1

S0

F

1-4

(Hz)

XTAL/CLKIN*

0

0

1

1

0

1

0

1

0.85

1.7

3.41

6.83

3.579MHz / 2

22

3.579MHz / 2

21

3.579MHz / 2

20

3.579MHz / 2

19

*NOTE F1-4 are a binary fraction of the master clock and therefore will vary

if the specified CLKIN frequency is altered.

Example 1

Thus if full scale differential dc voltages of +660mV and

-660mV are applied to V1 and V2 respectively ( 660mV is the

maximum differential voltage which can be connected to

channel 1 and channel 2) the expected output frequency is

calculated as follows.

Gain

F

1-4

V1

V2

=

=

=

=

1, G0 = G1 = 0

0.85Hz, S0 = S1 = 0

+660mV dc = 0.66 volts (RMS of dc = dc)

-660mV dc = 0.66 volts (RMS of dc = |dc|)

V

REF

=

2.5V (nominal reference value).

NOTE: If the on chip reference is used actual

output frequencies may vary from device to device

due to reference tolerence of ±8%.

Freq

5.7 0.66 0.66 1 0.85

2.5

2

=

=

034

.

Example 2

In this example ac voltages of ±660mV peak applied to V1 and

V2 then the expected output frequency is calculated as follows.

Gain

=

1, G0 = G1 = 0

F

1-4

=

0.85Hz, S0 = S1 = 0

V1

=

RMS of 660mV peak ac =

0.66 /

2

volts

V2

=

RMS of 660mV peak ac =

0.66 /

2

volts

V

REF

=

2.5V (nominal reference value).

NOTE: If the on chip reference is used actual

output frequencies may vary from device to device

due to reference tolerence of ±8%.

Freq

5.7 0.66 0.66 1 0.85

×

2

2 2.5

2

=

=

017

.

As can be seen from these two example calculations the

maximum output frequency for ac inputs is alway half of that

for dc input signals. Table II shows a complete listing of all

maximum output frequencies.

TABLE III

Max Frequency

for dc inputs (Hz)

Max Frequency

for ac inputs (Hz)

S1

S0

0

0

1

1

0

1

0

1

0.34

0.68

1.36

2.72

0.17

0.34

0.68

1.36

Frequency Output CF

The pulse output CF (Calibration Frequency) is intended for

use during calibration. The output pulse rate on CF can be up

to 128 times the pulse rate on F1 and F2. The lower the F1-4

frequency selected the higher the CF scaling. Table IV shows

how the two frequencies are related depending on the states of

the logic inputs S0, S1 and SFC. Because of its relatively high

pulse rate, the frequency at this logic output is proportional to

the instantaneous real power. As is the case with F1 and F2 the

frequency is derived from the output of the low pass filter after

multiplication. However because the output frequency is high,

this real power information is accumulated over a much shorter

time. Hence less averaging is carried out in the digital to

frequency conversion. With much less averaging of the real

power signal, the CF output is much more responsive to power

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD7755(中文) | Energy Metering IC with Pulse Output(帶脈沖輸出的高精度電子能量測量芯片) |

| AD7755 | Energy Metering IC with Pulse Output(帶脈沖輸出的高精度電子能量測量芯片) |

| AD775 | 8-Bit 20 MSPS, 60 mW Sampling A/D Converter(8位,20MSPS 60mW采樣A/D轉(zhuǎn)換器) |

| AD776 | 16-Bit 100 kSPS Oversampling ADC(16位100kSPS過采樣A/D轉(zhuǎn)換器) |

| AD7791 | Low Power, Buffered 24-Bit Sigma-Delta ADC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD7751AAN | 制造商:Analog Devices 功能描述: 制造商:Rochester Electronics LLC 功能描述:PRODUCT TO FREQUENCY CONV - Bulk |

| AD7751AAN-REF | 制造商:Analog Devices 功能描述: |

| AD7751AARS | 制造商:Rochester Electronics LLC 功能描述:PRODUCT TO FREQUENCY CONV - Bulk |

| AD7751ABRS | 制造商:AD 制造商全稱:Analog Devices 功能描述:Energy Metering IC With On-Chip Fault Detection |

| AD7751AN | 制造商:Rochester Electronics LLC 功能描述:PRODUCT TO FREQUENCY CONV - Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。