- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375169 > AAT3236IJS-30-T1 (Advanced Analogic Technologies, Inc.) 300mA CMOS High Performance LDO PDF資料下載

參數(shù)資料

| 型號: | AAT3236IJS-30-T1 |

| 廠商: | Advanced Analogic Technologies, Inc. |

| 英文描述: | 300mA CMOS High Performance LDO |

| 中文描述: | 300mA的LDO穩(wěn)壓器的CMOS高性能 |

| 文件頁數(shù): | 12/16頁 |

| 文件大小: | 448K |

| 代理商: | AAT3236IJS-30-T1 |

First the current duty cycle in percent must be

calculated:

% Peak Duty Cycle: X/100 = 378μs/4.61ms

% Peak Duty Cycle = 8.2%

The LDO Regulator will be under the 100mA load

for 91.8% of the 4.61ms period and have 500mA

peaks occurring for 8.2% of the time. Next, the

continuous nominal power dissipation for the

100mA load should be determined and then multi-

plied by the duty cycle to conclude the actual

power dissipation over time.

P

D(MAX)

= (V

IN

- V

OUT

)I

OUT

+ (V

IN

x I

GND

)

P

D(100mA)

= (4.2V - 3.3V)100mA + (4.2V x 150μA)

P

D(100mA)

= 90.6mW

P

D(91.8%D/C)

= %DC x P

D(100mA)

P

D(91.8%D/C)

= 0.918 x 90.6mW

P

D(91.8%D/C)

= 83.2mW

The power dissipation for 100mA load occurring for

91.8% of the duty cycle will be 83.2mW. Now the

power dissipation for the remaining 8.2% of the

duty cycle at the 500mA load can be calculated:

P

D(MAX)

= (V

IN

- V

OUT

)I

OUT

+ (V

IN

x I

GND

)

P

D(500mA)

= (4.2V - 3.3V)500mA + (4.2V x 150μA)

P

D(500mA)

= 450.6mW

P

D(8.2%D/C)

= %DC x P

D(500mA)

P

D(8.2%D/C)

= 0.082 x 450.6mW

P

D(8.2%D/C)

= 37mW

The power dissipation for 500mA load occurring for

8.2% of the duty cycle will be 37mW. Finally, the two

power dissipation levels can summed to determine

the total true power dissipation under the varied load.

P

D(total)

= P

D(100mA)

+ P

D(500mA)

P

D(total)

= 83.2mW + 37mW

P

D(total)

= 120.2mW

The maximum power dissipation for the AAT3236

operating at an ambient temperature of 25°C is

526mW. The device in this example will have a

total power dissipation of 120.2mW. This is well

within the thermal limits for safe operation of the

device.

Printed Circuit Board Layout

Recommendations

In order to obtain the maximum performance from

the AAT3236 LDO regulator, very careful attention

must be considered in regard to the printed circuit

board (PCB) layout. If grounding connections are

not properly made, power supply ripple rejection,

low output self noise and transient response can be

compromised.

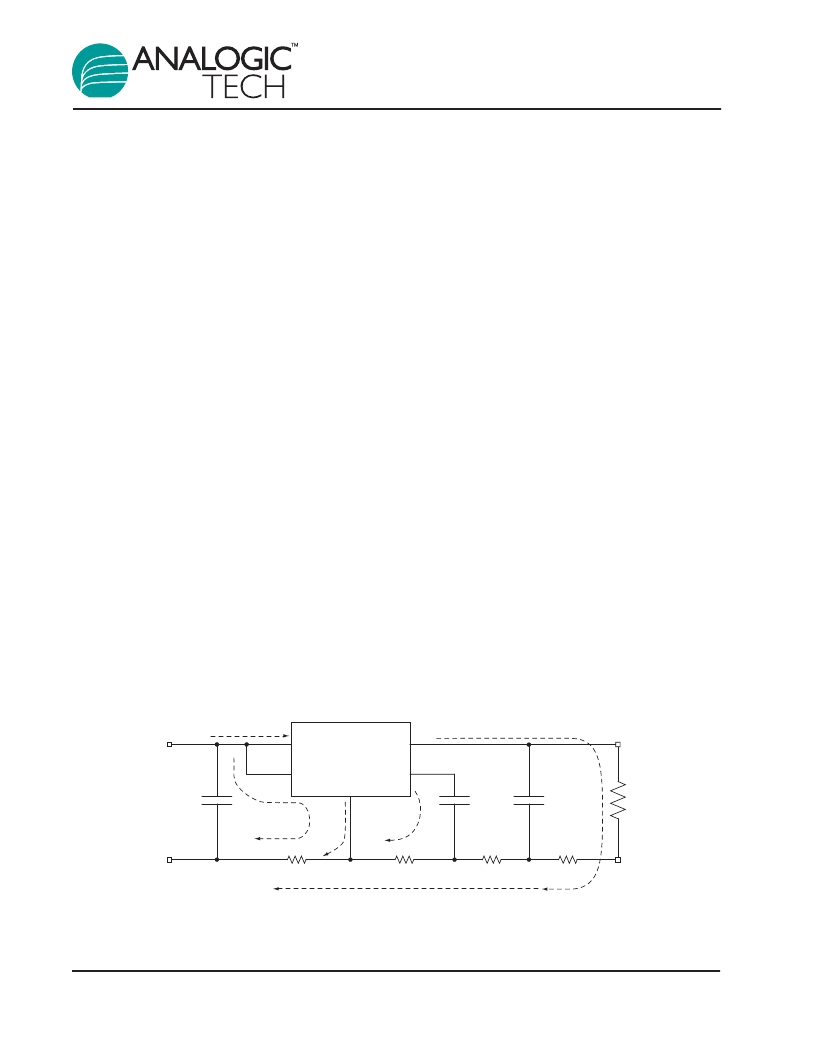

Figure 18 shows a common LDO regulator layout

scheme. The LDO Regulator, external capacitors

(C

IN

, C

OUT

and C

BYP

) and the load circuit are all

connected to a common ground plane. This type of

layout will work in simple applications where good

power supply ripple rejection and low self noise are

not a design concern. For high performance appli-

cations, this method is not recommended.

AAT3236

300mA CMOS High Performance LDO

12

3236.2001.11.0.9

Figure 18: Common LDO Regulator Layout with C

BYP

Ripple feedback loop

LDO

Regulator

C

BYP

C

OUT

R

TRACE

R

TRACE

R

TRACE

R

TRACE

C

IN

R

LOAD

V

IN

EN

GND

V

OUT

BYP

I

LOAD

I

RIPPLE

I

IN

V

IN

GND

DC INPUT

I

GND

C

BYP

GND

LOOP

I

LOAD

return + noise and ripple

I

BYP

+ noise

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AAT3236IJS-33-T1 | 300mA CMOS High Performance LDO |

| AAT3236IJS-35-T1 | 300mA CMOS High Performance LDO |

| AAT3236IGV-27-T1 | 300mA CMOS High Performance LDO |

| AAT3237 | 300mA MicroPower⑩ LDO with PowerOK |

| AAT3237IGU-2.3-T1 | 300mA MicroPower⑩ LDO with PowerOK |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AAT3236IJS-33-T1 | 制造商:ANALOGICTECH 制造商全稱:Advanced Analogic Technologies 功能描述:300mA CMOS High Performance LDO |

| AAT3236IJS-35-T1 | 制造商:ANALOGICTECH 制造商全稱:Advanced Analogic Technologies 功能描述:300mA CMOS High Performance LDO |

| AAT3237 | 制造商:ANALOGICTECH 制造商全稱:Advanced Analogic Technologies 功能描述:300mA MicroPower⑩ LDO with PowerOK |

| AAT3237BIGU-2.6-T1 | 制造商:Skyworks Solutions Inc 功能描述:300mA MicroPower LDO-Linear Regulator |

| AAT3237BIGU-2.85-T1 | 制造商:Skyworks Solutions Inc 功能描述:300mA MicroPower LDO-Linear Regulator |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。