- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄294482 > 85304AG-01 (INTEGRATED DEVICE TECHNOLOGY INC) 85304 SERIES, LOW SKEW CLOCK DRIVER, 5 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO20 PDF資料下載

參數(shù)資料

| 型號(hào): | 85304AG-01 |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時(shí)鐘及定時(shí) |

| 英文描述: | 85304 SERIES, LOW SKEW CLOCK DRIVER, 5 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO20 |

| 封裝: | 6.50 X 4.40 MM, 0.92 MM PITCH, MO-153, TSSOP-20 |

| 文件頁(yè)數(shù): | 6/15頁(yè) |

| 文件大小: | 760K |

| 代理商: | 85304AG-01 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)當(dāng)前第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)

ICS85304-01

LOW SKEW, 1-TO-5 DIFFERENTIAL-TO- 3.3V LVPECL FANOUT BUFFER

IDT / ICS 3.3V LVPECL FANOUT BUFFER

14

ICS85304AG-01 REV. E JULY 8, 2008

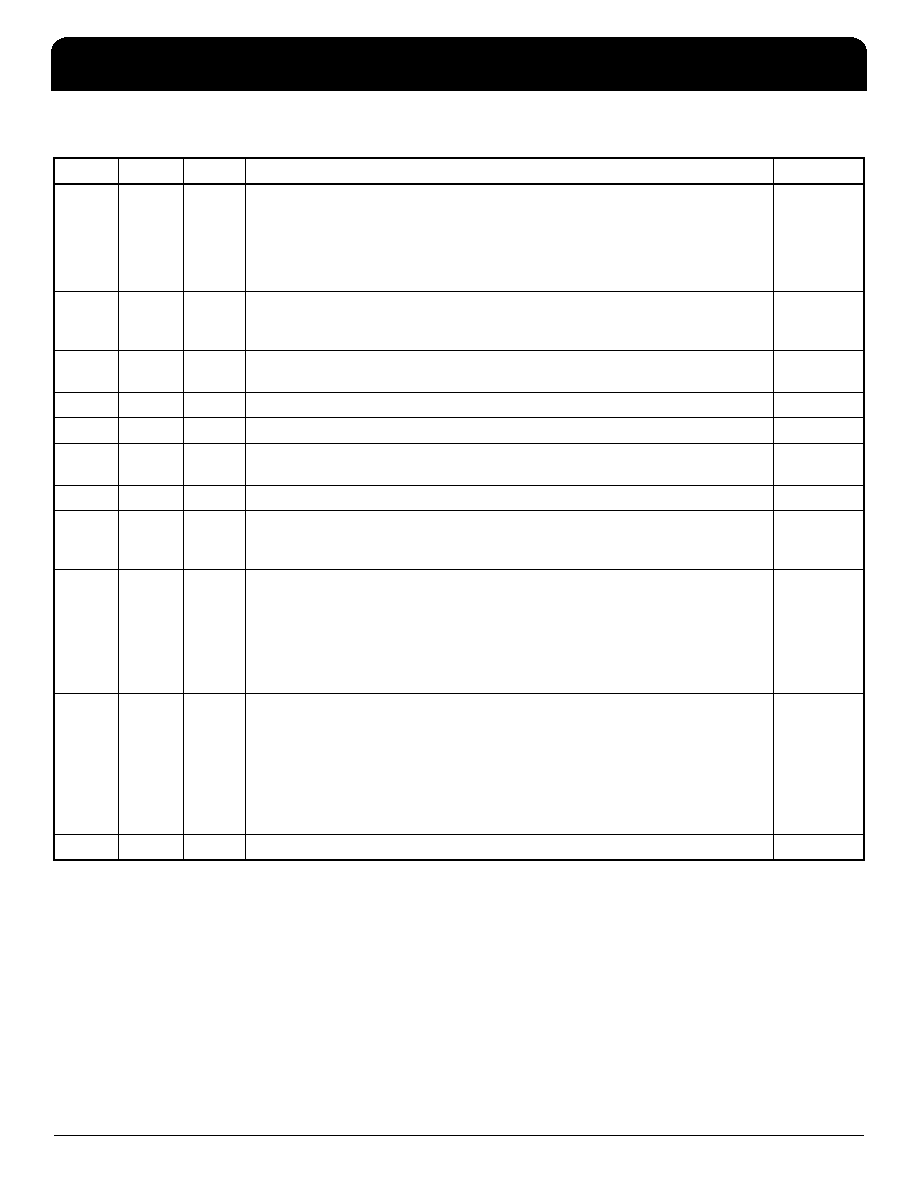

Revision History Sheet

Rev

Table

Page

Description of Change

Date

A

T4B

T4D

T5

4

5

VCMR values changed from 1.5V min. to 0.5V min.; VDD max. to VCC - 0.85V max.

VOH values changed from 1.9A min. to VCC - 1.4A min.; 2.3A max. to VCC - 1.0A.

VOL values changed from 1.2A min. to VCC - 2.0A; 1.6A max. to VCC - 1.7A max.

Replaced tpLH and tpHL with tPD at the same values.

Replaced tPW and values of tCYCLE/2 - 40 min., tCYCLE/2 typ., tCYCLE/2 + 40 max.

with odc at values of 48% min., 50% typ., 52% max.

5/14/01

B

T4D

T5

5

LVPECL DC Characteristics Table - added IIH, IIL, VPP, and VCMR rows.

AC Characteristics Table - tR and tF values changed from 275ps min to 300ps min;

650ps max. to 700ps max.

5/22/01

C

T4D

5

Differential DC Characteristics Table - VCMR values changed from VCC - 0.85V max. to

VCC.

8/21/01

C

3

Revised Figure 1, CLK_EN Timing Diagram.

10/17/01

C

3

Revised Figure 1, CLK_EN Timing Diagram.

11/2/01

C

T3B

3

Revised Inputs heading from CLK or CLK, nPCLK or nPCLK to CLK or PCLK, nCLK or

nPCLK.

12/28/01

C

8

Added Termination for LVEPCL Output section.

5/30/02

C

6

7

3.3V Output Load Test Circuit Diagram - corrected VEE = -1.3V ± 0.135V to

VEE = -1.3V ± 0.165V.

Updated Output Rise/Fall Time Diagram.

8/26/02

D

T2

T9

1

2

4

6

8

9

14

Added Lead-Free bullet in Features section.

Pin Characteristics table - changed CIN 4pF max. to 4pF typical.

Absolute Maximum Ratings, updated Outputs rating.

Updated Parameter Measurement Information.

Added Differential Clock Input Interface section.

Added LVPECL Clock Input Interface section.

Ordering Information table - added Lead Free part number.

6/17/04

E

T9

8

9

10

13

Per Document Errata, NEN-08-03, corrected name of PCLK/nPCLK to CLK1/nCLK1

and changed CLK/nCLK to CLK0/nCLK0 throughout the datasheet.

Updated Differential Clock Input Interface section.

Deleted LVPECL Clock Input Interface section.

Added Recommendations for Unused Input and Output Pins section.

Power Considerations - corrected Junction Temperature calculations.

Ordering Information Table - corrected marking.

Updated format throughout the datasheet.

6/20/08

E

3

Corrected Figure 1, CLK_EN Timing Diagram.

7/8/08

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 85304AG-01T | 85304 SERIES, LOW SKEW CLOCK DRIVER, 5 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO20 |

| 853134 | 147 CONTACT(S), MALE, STRAIGHT TWO PART BOARD CONNECTOR, PRESS FIT |

| 8532AY-01LFT | 8532 SERIES, LOW SKEW CLOCK DRIVER, 17 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP52 |

| 8535AG-21 | 8535 SERIES, LOW SKEW CLOCK DRIVER, 2 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO14 |

| 8535AG-21LF | 8535 SERIES, LOW SKEW CLOCK DRIVER, 2 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO14 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 85304AG-01LF | 功能描述:時(shí)鐘緩沖器 1:5 LVPECL Fanout Buffer RoHS:否 制造商:Texas Instruments 輸出端數(shù)量:5 最大輸入頻率:40 MHz 傳播延遲(最大值): 電源電壓-最大:3.45 V 電源電壓-最小:2.375 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LLP-24 封裝:Reel |

| 85304AG-01LFT | 功能描述:時(shí)鐘驅(qū)動(dòng)器及分配 1:5 LVPECL Fanout Buffer RoHS:否 制造商:Micrel 乘法/除法因子:1:4 輸出類型:Differential 最大輸出頻率:4.2 GHz 電源電壓-最大: 電源電壓-最小:5 V 最大工作溫度:+ 85 C 封裝 / 箱體:SOIC-8 封裝:Reel |

| 85304AG-01T | 制造商:Integrated Device Technology Inc 功能描述:CLOCK DRVR 2-IN LVPECL 20TSSOP - Tape and Reel |

| 85304AGI-01LF | 功能描述:時(shí)鐘驅(qū)動(dòng)器及分配 RoHS:否 制造商:Micrel 乘法/除法因子:1:4 輸出類型:Differential 最大輸出頻率:4.2 GHz 電源電壓-最大: 電源電壓-最小:5 V 最大工作溫度:+ 85 C 封裝 / 箱體:SOIC-8 封裝:Reel |

| 85304AGI-01LFT | 制造商:Integrated Device Technology Inc 功能描述:NETCOM - Bulk |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。