- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄298557 > 7P512FLG0801C20 (WHITE ELECTRONIC DESIGNS CORP) 256K X 16 FLASH 12V PROM CARD, 200 ns, XMA68 PDF資料下載

參數(shù)資料

| 型號: | 7P512FLG0801C20 |

| 廠商: | WHITE ELECTRONIC DESIGNS CORP |

| 元件分類: | PROM |

| 英文描述: | 256K X 16 FLASH 12V PROM CARD, 200 ns, XMA68 |

| 封裝: | CARD-68 |

| 文件頁數(shù): | 6/11頁 |

| 文件大小: | 344K |

| 代理商: | 7P512FLG0801C20 |

PCMCIA Flash Memory Card

FLG Series

4

White Electronic Designs

June, 2003

Rev. 4

White Electronic Designs Corp. reserves the right to change products or specications without notice.

White Electronic Designs Corporation (602) 437-1520 www.wedc.com

CARD SIGNAL DESCRIPTION

Symbol

Type

Name and Function

A0 - A25

INPUT

ADDRESS INPUTS: A0 through A25 enable direct addressing of up to 64MB of memory on the card. Signal A0 is not used in

word access mode. The memory will wrap at the card density boundary (see PINOUT, note 3). The system should not try to

access memory beyond the card density. A25 is the most signicant bit. A23 - A25 are not connected.

DQ0 - DQ15

INPUT/OUTPUT

DATA INPUT/OUTPUT: DQ0 THROUGH DQ15 constitute the bi-directional databus. DQ0 - Dq7 constitute the lower (even) byte

and DQ8 - DQ15 the upper (odd) byte. DQ15 is the MSB.

CE1#, CE2#

INPUT

CARD ENABLE 1 AND 2: CE1 enables even byte accesses, CE2 enables odd byte accesses. Multiplexing A0, CE1 and CE2

allows 8-bit hosts to access all data on DQ0 - DQ7.

OE#

INPUT

OUTPUT ENABLE: Active low signal gating read data from the memory card.

WE#

INPUT

WRITE ENABLE: Active low signal gating write data to the memory card.

RDY/BSY#

N.C.

READY/BUSY OUTPUT: Indicates status of internally timed erase or program algorithms. This signal is not

connected.

CD1#, CD2#

OUTPUT

CARD DETECT 1 and 2: Provide card insertion detection. These signals are connected to ground internally on the memory

card. The host shall monitor these signals to detect card insertion (pulled-up on host side).

WP

OUTPUT

WRITE PROTECT: Write protect reects the status of the Write Protect switch on the memory card. WP set to high = write

protected, providing internal hardware write lockout to the Flash array.If card does not include optional write protect switch, this

signal will be pulled low internally indicating write protect = “off”.

VPP1

PROGRAM/ERASE POWER SUPPLY: Provides programming voltages 12.0V for lower byte (D0 - D7) memory components.

VPP2

PROGRAM/ERASE POWER SUPPLY: Provides programming voltages 12.0V for lower byte (D8 - D15) memory components.

VCC

CARD POWER SUPPLY: 5.0V

GND

CARD GROUND

REG#

INPUT

ATTRIBUTE MEMORY SELECT : Active low signal, enables access to Attribute Memory Plane, occupied

by Card Information Structure and Card Registers.

RST#

N.C.

RESET: Active high signal for placing card in Power-on default state. This signal is not connected.

WAIT#

OUTPUT

WAIT: This signal is pulled high internally for compatibility. No wait states are generated.

BVD1, BVD2

OUTPUT

BATTERY VOLTAGE DETECT: These signals are pulled high to maintain SRAM card compatibility.

VS1, VS2

OUTPUT

VOLTAGE SENSE: Noties the host socket of the card’s VCC requirements. VS1 and VS2 are open to indicate a 5V card has

been inserted.

RFU

RESERVED FOR FUTURE USE

N.C.

NO INTERNAL CONNECTION TO CARD: pin may be driven or left oating

* Require proper programming voltages (Vpp1, Vpp2). Program or Erase with an invalid Vpp should not be attempted.

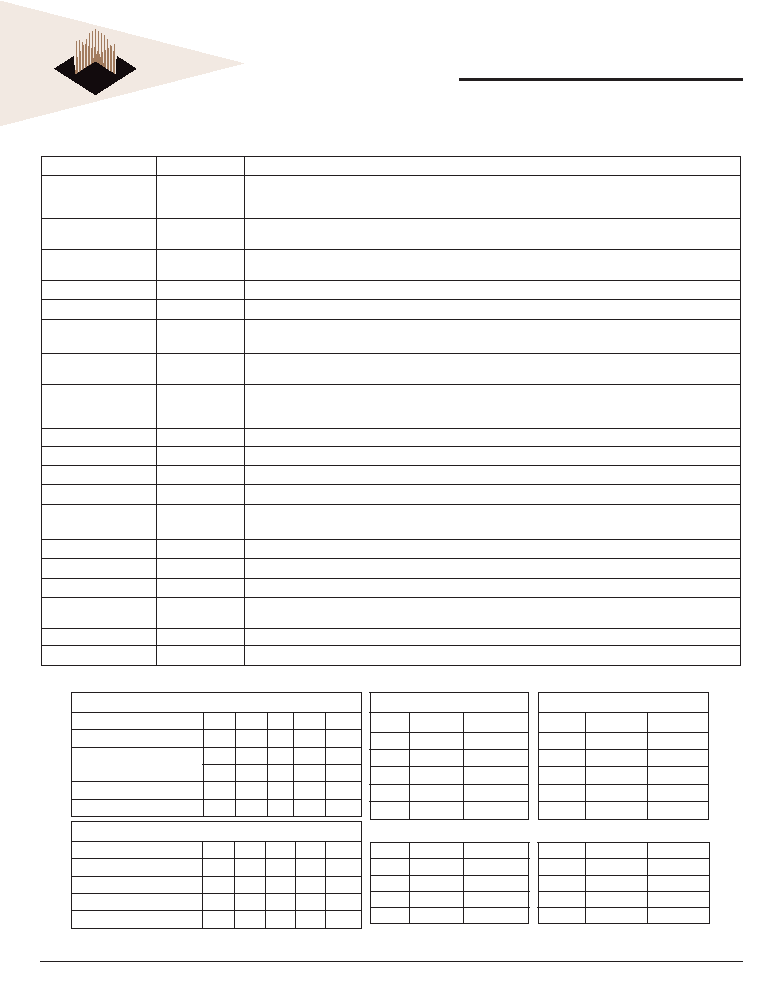

FUNCTIONAL TRUTH TABLE

READ function

Function Mode

CE2# CE1# A0 OE# WE#

Standby Mode

H

X

Byte Access (8 bits)

H

L

H

L

H

L

H

Word Access (16 bits)

L

X

L

H

Odd-Byte Only Access

L

H

X

L

H

Common Memory

REG#

D15-D8

D7-D0

X

High-Z

H

High-Z

Even-Byte

H

High-Z

Odd-Byte

H

Odd-Byte Even-Byte

H

Odd-Byte

High-Z

Attribute Memory

REG#

D15-D8

D7-D0

X

High-Z

L

High-Z

Even-Byte

L

High-Z

Not Valid

L

Not Valid

Even-Byte

L

Not Valid

High-Z

WRITE function*

Standby Mode

H

X

Byte Access (8 bits)

H

L

H

L

H

L

H

L

Word Access (16 bits)

L

X

H

L

Odd-Byte Only Access

L

H

X

H

L

X

H

X

Even-Byte

H

X

Odd-Byte

H

Odd-Byte

Even-Byte

H

Odd-Byte

X

L

X

Even-Byte

L

X

L

X

Even-Byte

L

X

相關PDF資料 |

PDF描述 |

|---|---|

| 7P512FLG1100C20 | 256K X 16 FLASH 12V PROM CARD, 200 ns, XMA68 |

| 7P512FLG1300I20 | 256K X 16 FLASH 12V PROM CARD, 200 ns, XMA68 |

| 7P512FLG1700C20 | 256K X 16 FLASH 12V PROM CARD, 200 ns, XMA68 |

| 7P512FLG0602I15 | 256K X 16 FLASH 12V PROM CARD, 150 ns, XMA68 |

| 7P512FLG1302I15 | 256K X 16 FLASH 12V PROM CARD, 150 ns, XMA68 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| 7P601V330K042 | 制造商:CDE 制造商全稱:Cornell Dubilier Electronics 功能描述:Type 7P 55 ∑C Photoflash, High-Energy, Long Life, Aluminum |

| 7P601V360A032 | 功能描述:鋁質電解電容器-管理單元 600uF 360V PHOTO RoHS:否 制造商:Nichicon 電容:470 uF 容差:20 % 電壓額定值:450 V ESR: 工作溫度范圍:- 25 C to + 105 C 系列:AR 直徑:35 mm 長度:45 mm 引線間隔:10 mm 產(chǎn)品:General Purpose Electrolytic Capacitors |

| 7P701V330A042 | 制造商:CDE 制造商全稱:Cornell Dubilier Electronics 功能描述:Type 7P 55 ∑C Photoflash, High-Energy, Long Life, Aluminum |

| 7P701V360A042 | 制造商:CDE 制造商全稱:Cornell Dubilier Electronics 功能描述:Type 7P 55 ∑C Photoflash, High-Energy, Long Life, Aluminum |

| 7P801V330A042 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Photoflash, High-Energy, Long Life, Aluminum |

發(fā)布緊急采購,3分鐘左右您將得到回復。