- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄222840 > 74VHC112MTC (FAIRCHILD SEMICONDUCTOR CORP) Dual J-K Flip-Flops with Preset and Clear PDF資料下載

參數(shù)資料

| 型號(hào): | 74VHC112MTC |

| 廠(chǎng)商: | FAIRCHILD SEMICONDUCTOR CORP |

| 元件分類(lèi): | 鎖存器 |

| 英文描述: | Dual J-K Flip-Flops with Preset and Clear |

| 中文描述: | AHC/VHC SERIES, DUAL NEGATIVE EDGE TRIGGERED J-K FLIP-FLOP, COMPLEMENTARY OUTPUT, PDSO16 |

| 封裝: | 4.40 MM, MO-153, TSSOP-16 |

| 文件頁(yè)數(shù): | 5/9頁(yè) |

| 文件大小: | 264K |

| 代理商: | 74VHC112MTC |

74VHC112

Dual

J-K

Flip-Flops

with

Preset

and

Clear

1995 Fairchild Semiconductor Corporation

www.fairchildsemi.com

74VHC112 Rev. 1.2

5

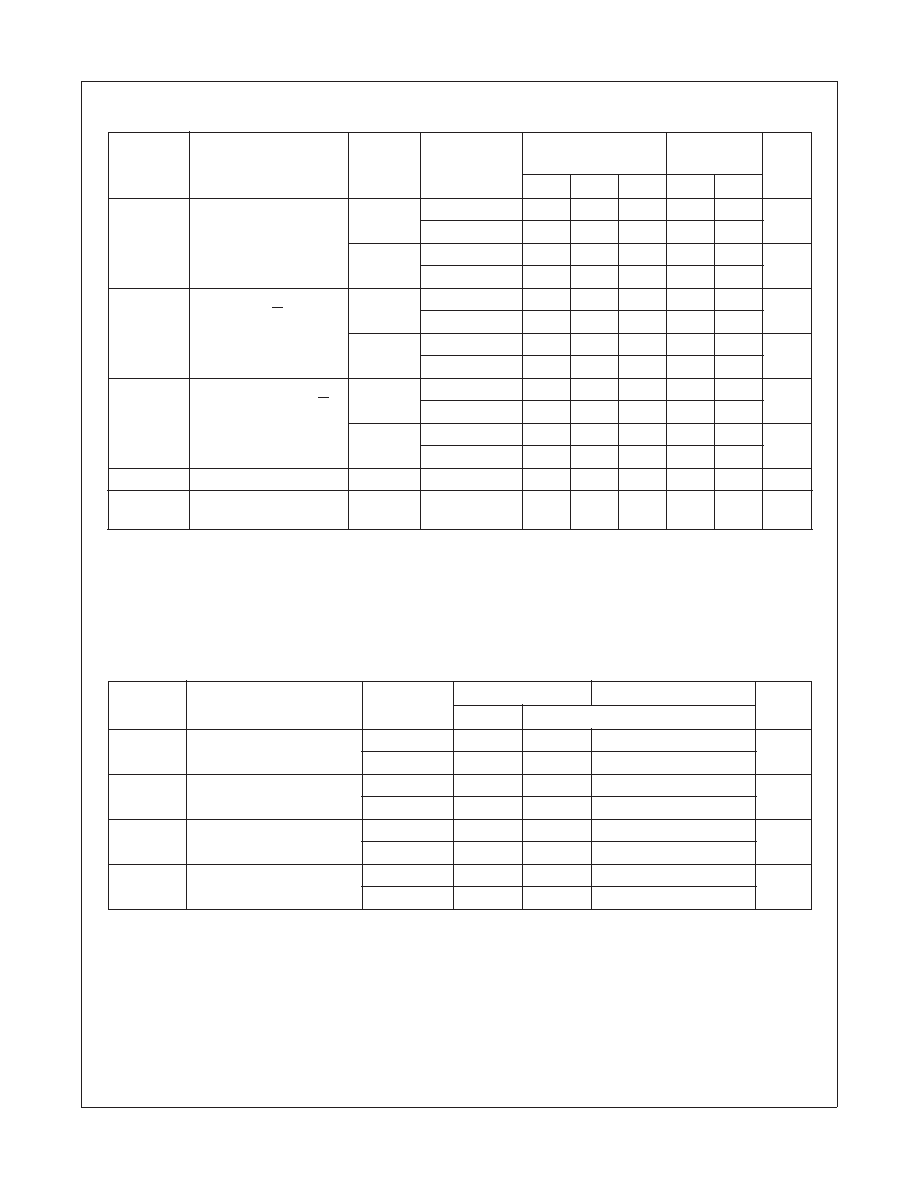

AC Electrical Characteristics

Note:

2. CPD is defined as the value of the internal equivalent capacitance which is calculated from the operating

current consumption without load. Average operating current can be obtained from the equation:

ICC (opr.) = CPD VCC fIN + ICC / 4 (per F/F), and the total CPD when n pcs of the Flip-Flop operate can be calculated

by the following equation: CPD (total) = 30 + 14 n

AC Operating Requirements

Note:

3. VCC is 3.3 ± 0.3V or 5.0 ± 0.5V.

Symbol

Parameter

VCC (V)

Conditions

TA = 25°C

TA = –40°C

to +85°C

Units

Min.

Typ.

Max.

Min.

Max.

fMAX

Maximum Clock

Frequency

3.3 ± 0.3

CL = 15pF

110

150

100

MHz

CL = 50pF

90

120

80

5.0 ± 0.5

CL = 15pF

150

200

135

MHz

CL = 50pF

120

185

110

tPLH, tPHL

Propagation Delay Time

(CP to Qn or Qn)

3.3 ± 0.3

CL = 15pF

8.5

11.0

1.0

13.4

ns

CL = 50pF

10.0

15.0

1.0

16.5

5.0 ± 0.5

CL = 15pF

5.1

7.3

1.0

8.8

ns

CL = 50pF

6.3

10.5

1.0

12.0

tPLH, tPHL

Propagation Delay Time

(PR or CLR to Qn or Qn)

3.3 ± 0.3

CL = 15pF

6.7

10.2

1.0

11.7

ns

CL = 50pF

9.7

13.5

1.0

15.0

5.0 ± 0.5

CL = 15pF

4.6

6.7

1.0

8.0

ns

CL = 50pF

6.4

9.5

1.0

11.0

CIN

Input Capacitance

VCC = Open

4

10

pF

CPD

Power Dissipation

Capacitance

(2)

18

pF

Symbol

Parameter

VCC (V)

(3)

TA = 25°C

TA = –40°C to +85°C

Units

Typ.

Guaranteed Minimum

tW

Minimum Pulse Width

(CP or CLR or PR)

3.3

5.0

ns

5.0

tS

Minimum Setup Time

(Jn or Kn to CPn)

3.3

5.0

ns

5.0

4.0

tH

Minimum Hold Time

(Jn or Kn to CPn)

3.3

1.0

ns

5.0

1.0

tREC

Minimum Recovery Time

(CLR or PR to CP)

3.3

6.0

ns

5.0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 74VHC112SJ | Dual J-K Flip-Flops with Preset and Clear |

| 74VHC112N | Dual J-K Flip-Flops with Preset and Clear |

| 74VHC123AM | Dual Retriggerable Monostable Multivibrator |

| 74VHC123AMTC | Automotive Catalog Dual D-Type Positive-Edge-Triggered Flip-Flops With Clear and Preset 14-TSSOP -40 to 125 |

| 74VHC123AN | Dual Retriggerable Monostable Multivibrator |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 74VHC112MTC_NL | 功能描述:觸發(fā)器 Dual J-K Flip-Flops with Preset and Clear RoHS:否 制造商:Texas Instruments 電路數(shù)量:2 邏輯系列:SN74 邏輯類(lèi)型:D-Type Flip-Flop 極性:Inverting, Non-Inverting 輸入類(lèi)型:CMOS 輸出類(lèi)型: 傳播延遲時(shí)間:4.4 ns 高電平輸出電流:- 16 mA 低電平輸出電流:16 mA 電源電壓-最大:5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:X2SON-8 封裝:Reel |

| 74VHC112MTC_Q | 功能描述:觸發(fā)器 Dual J-K Flip-Flops RoHS:否 制造商:Texas Instruments 電路數(shù)量:2 邏輯系列:SN74 邏輯類(lèi)型:D-Type Flip-Flop 極性:Inverting, Non-Inverting 輸入類(lèi)型:CMOS 輸出類(lèi)型: 傳播延遲時(shí)間:4.4 ns 高電平輸出電流:- 16 mA 低電平輸出電流:16 mA 電源電壓-最大:5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:X2SON-8 封裝:Reel |

| 74VHC112MTCX | 功能描述:觸發(fā)器 Dual J-K Flip-Flops RoHS:否 制造商:Texas Instruments 電路數(shù)量:2 邏輯系列:SN74 邏輯類(lèi)型:D-Type Flip-Flop 極性:Inverting, Non-Inverting 輸入類(lèi)型:CMOS 輸出類(lèi)型: 傳播延遲時(shí)間:4.4 ns 高電平輸出電流:- 16 mA 低電平輸出電流:16 mA 電源電壓-最大:5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:X2SON-8 封裝:Reel |

| 74VHC112MTCX_NL | 功能描述:觸發(fā)器 FINISHED GOOD RoHS:否 制造商:Texas Instruments 電路數(shù)量:2 邏輯系列:SN74 邏輯類(lèi)型:D-Type Flip-Flop 極性:Inverting, Non-Inverting 輸入類(lèi)型:CMOS 輸出類(lèi)型: 傳播延遲時(shí)間:4.4 ns 高電平輸出電流:- 16 mA 低電平輸出電流:16 mA 電源電壓-最大:5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:X2SON-8 封裝:Reel |

| 74VHC112MX | 功能描述:觸發(fā)器 Dual J-K Flip-Flops RoHS:否 制造商:Texas Instruments 電路數(shù)量:2 邏輯系列:SN74 邏輯類(lèi)型:D-Type Flip-Flop 極性:Inverting, Non-Inverting 輸入類(lèi)型:CMOS 輸出類(lèi)型: 傳播延遲時(shí)間:4.4 ns 高電平輸出電流:- 16 mA 低電平輸出電流:16 mA 電源電壓-最大:5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:X2SON-8 封裝:Reel |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。