- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375082 > 74LVTH32373GX (FAIRCHILD SEMICONDUCTOR CORP) Low Voltage 32-Bit Transparent Latch with 3-STATE Outputs (Preliminary) PDF資料下載

參數(shù)資料

| 型號: | 74LVTH32373GX |

| 廠商: | FAIRCHILD SEMICONDUCTOR CORP |

| 元件分類: | 通用總線功能 |

| 英文描述: | Low Voltage 32-Bit Transparent Latch with 3-STATE Outputs (Preliminary) |

| 中文描述: | LVT SERIES, QUAD 8-BIT DRIVER, TRUE OUTPUT, PBGA96 |

| 封裝: | 5.50 MM, PLASTIC, MO-205, FBGA-96 |

| 文件頁數(shù): | 2/6頁 |

| 文件大小: | 160K |

| 代理商: | 74LVTH32373GX |

Preliminary

www.fairchildsemi.com

2

7

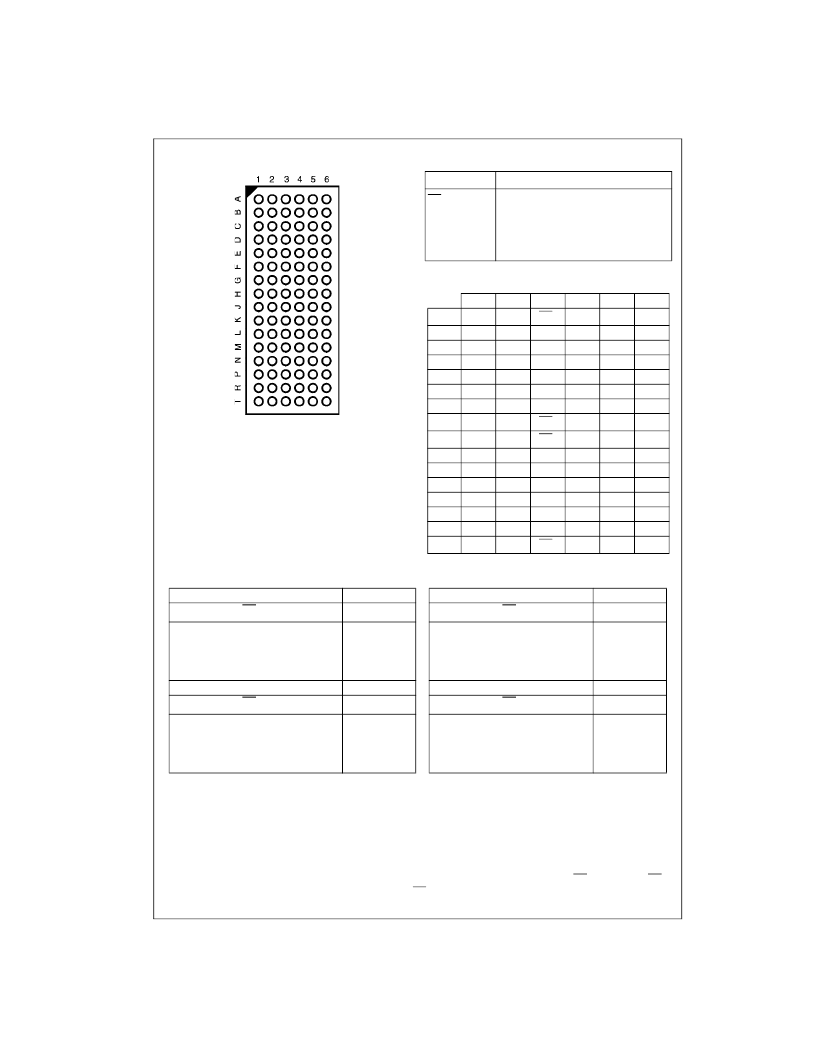

Connection Diagram

(Top Thru View)

Pin Descriptions

FBGA Pin Assignments

Truth Table

H

=

HIGH Voltage Level

L

=

LOW Voltage Level

X

=

Immaterial

Z

=

HIGH Impedance

O

o

=

Previous O

o

prior to HIGH-to-LOW transition of LE

Functional Description

The LVT32373 and LVTH32373 contain thirty-two D-type latches with 3-STATE standard outputs. The device is byte con-

trolled with each byte functioning identically, but independent of the other. Control pins can be shorted together to obtain full

32-bit operation. The following description applies to each byte. When the Latch Enable (LE

n

) input is HIGH, data on the D

n

enters the latches. In this condition the latches are transparent, i.e, a latch output will change states each time its D input

changes. When LE

n

is LOW, the latches store information that was present on the D inputs a setup time preceding the

HIGH-to-LOW transition of LE

n

. The 3-STATE standard outputs are controlled by the Output Enable (OE

n

) input. When OE

n

is LOW, the standard outputs are in the 2-state mode. When OE

n

is HIGH, the standard outputs are in the high impedance

mode but this does not interfere with entering new data into the latches.

Pin Names

Description

OE

n

LE

n

I

0

–I

31

O

0

–O

31

Output Enable Input (Active LOW)

Latch Enable Input

Inputs

3-STATE Outputs

1

2

3

4

5

6

A

B

C

D

E

F

G

O

1

O

3

O

5

O

7

O

9

O

11

O

13

O

14

O

17

O

19

O

21

O

23

O

25

O

27

O

29

O

30

O

0

O

2

O

4

O

6

O

8

O

10

O

12

O

15

O

16

O

18

O

20

O

22

O

24

O

26

O

28

O

31

OE

1

GND

V

CC1

GND

GND

V

CC1

GND

LE

1

GND

V

CC1

GND

GND

V

CC1

GND

I

0

I

2

I

4

I

6

I

8

I

10

I

12

I

15

I

16

I

18

I

20

I

22

I

24

I

26

I

28

I

31

I

1

I

3

I

5

I

7

I

9

I

11

I

13

I

14

I

17

I

19

I

21

I

23

I

25

I

27

I

29

I

30

H

OE

2

OE

3

GND

V

CC2

GND

GND

V

CC2

GND

LE

2

LE

3

GND

V

CC2

GND

GND

V

CC2

GND

J

K

L

M

N

P

R

T

OE

4

LE

4

Inputs

Outputs

Inputs

Outputs

CP

1

X

H

H

L

OE

1

H

L

L

L

Inputs

I

0

–

I

7

X

L

H

X

O

0

–

O

7

Z

L

H

O

0

Outputs

CP

2

X

H

H

L

OE

2

H

L

L

L

Inputs

I

8

–

I

15

X

L

H

X

O

8

–

O

15

Z

L

H

O

0

Outputs

CP

3

X

H

H

L

OE

3

H

L

L

L

I

16

–

I

23

X

L

H

X

O

16

–

O

23

Z

L

H

O

0

CP

4

X

H

H

L

OE

4

H

L

L

L

I

24

–

I

31

X

L

H

X

O

24

–

O

31

Z

L

H

O

0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 74LVT32374G | Octal Transparent D-Type Latches With 3-State Outputs 20-SSOP -40 to 85 |

| 74LVT32374 | Low Voltage 32-Bit D-Type Flip-Flop with 3-STATE Outputs |

| 74LVTH32374 | Low Voltage 32-Bit D-Type Flip-Flop with 3-STATE Outputs |

| 74LVTH32374G | Quadruple Positive-NOR Gates With Schmitt-Trigger Inputs 14-SO -40 to 85 |

| 74LVTH125M | Low Voltage Quad Buffer with 3-STATE Outputs |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 74LVTH32374GX | 功能描述:觸發(fā)器 D-Type Flip-Flop LV 32Bit RoHS:否 制造商:Texas Instruments 電路數(shù)量:2 邏輯系列:SN74 邏輯類型:D-Type Flip-Flop 極性:Inverting, Non-Inverting 輸入類型:CMOS 輸出類型: 傳播延遲時間:4.4 ns 高電平輸出電流:- 16 mA 低電平輸出電流:16 mA 電源電壓-最大:5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:X2SON-8 封裝:Reel |

| 74LVTH373MTC | 功能描述:閉鎖 Octal Trans Latch RoHS:否 制造商:Micrel 電路數(shù)量:1 邏輯類型:CMOS 邏輯系列:TTL 極性:Non-Inverting 輸出線路數(shù)量:9 高電平輸出電流: 低電平輸出電流: 傳播延遲時間: 電源電壓-最大:12 V 電源電壓-最小:5 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:SOIC-16 封裝:Reel |

| 74LVTH373MTCX | 功能描述:閉鎖 Octal Trans Latch RoHS:否 制造商:Micrel 電路數(shù)量:1 邏輯類型:CMOS 邏輯系列:TTL 極性:Non-Inverting 輸出線路數(shù)量:9 高電平輸出電流: 低電平輸出電流: 傳播延遲時間: 電源電壓-最大:12 V 電源電壓-最小:5 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:SOIC-16 封裝:Reel |

| 74LVTH373MTCX_NL | 功能描述:閉鎖 LV OCTAL TRANSP LATCH BH RoHS:否 制造商:Micrel 電路數(shù)量:1 邏輯類型:CMOS 邏輯系列:TTL 極性:Non-Inverting 輸出線路數(shù)量:9 高電平輸出電流: 低電平輸出電流: 傳播延遲時間: 電源電壓-最大:12 V 電源電壓-最小:5 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:SOIC-16 封裝:Reel |

| 74LVTH373SJ | 功能描述:閉鎖 Octal Trans Latch RoHS:否 制造商:Micrel 電路數(shù)量:1 邏輯類型:CMOS 邏輯系列:TTL 極性:Non-Inverting 輸出線路數(shù)量:9 高電平輸出電流: 低電平輸出電流: 傳播延遲時間: 電源電壓-最大:12 V 電源電壓-最小:5 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:SOIC-16 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。