- 您現(xiàn)在的位置:買賣IC網 > PDF目錄375076 > 74LCX16841MEA (FAIRCHILD SEMICONDUCTOR CORP) Low Voltage 20-Bit Transparent Latch with 5V Tolerant Inputs and Outputs PDF資料下載

參數(shù)資料

| 型號: | 74LCX16841MEA |

| 廠商: | FAIRCHILD SEMICONDUCTOR CORP |

| 元件分類: | 通用總線功能 |

| 英文描述: | Low Voltage 20-Bit Transparent Latch with 5V Tolerant Inputs and Outputs |

| 中文描述: | LVC/LCX/Z SERIES, DUAL 10-BIT DRIVER, TRUE OUTPUT, PDSO56 |

| 封裝: | 0.300 INCH, MO-118, SSOP-56 |

| 文件頁數(shù): | 1/8頁 |

| 文件大?。?/td> | 91K |

| 代理商: | 74LCX16841MEA |

2001 Fairchild Semiconductor Corporation

DS012578

www.fairchildsemi.com

October 1995

Revised April 2001

7

74LCX16841

Low Voltage 20-Bit Transparent Latch

with 5V Tolerant Inputs and Outputs

General Description

The LCX16841 contains twenty non-inverting latches with

3-STATE outputs and is intended for bus oriented applica-

tions. The device is byte controlled. The flip-flops appear

transparent to the data when the Latch Enable (LE) is

HIGH. When LE is LOW, the data that meets the setup time

is latched. Data appears on the bus when the Output

Enable (OE) is LOW. When OE is HIGH, the outputs are in

a high impedance state.

The LCX16841 is designed for low voltage (2.5V or 3.3V)

V

CC

applications with capability of interfacing to a 5V signal

environment.

The LCX16841 is fabricated with an advanced CMOS tech-

nology to achieve high speed operation while maintaining

CMOS low power dissipation.

Features

I

5V tolerant inputs and outputs

I

2.3V–3.6V V

CC

specifications provided

I

5.5 ns t

PD

max (V

CC

=

3.3V), 20

μ

A I

CC

max

I

Power down high impedance inputs and outputs

I

Supports live insertion/withdrawal (Note 1)

I

±

24 mA output drive (V

CC

=

3.0V)

I

Implements patented noise/EMI reduction circuitry

I

Latch-up performance exceeds 500 mA

I

ESD performance:

Human body model

>

2000V

Machine model

>

200V

Note 1:

To ensure the high-impedance state during power up or down, OE

should be tied to V

CC

through a pull-up resistor: the minimum value or the

resistor is determined by the current-sourcing capability of the driver.

Ordering Code:

Devices also available in Tape and Reel. Specify by appending suffix letter

“

X

”

to the ordering code.

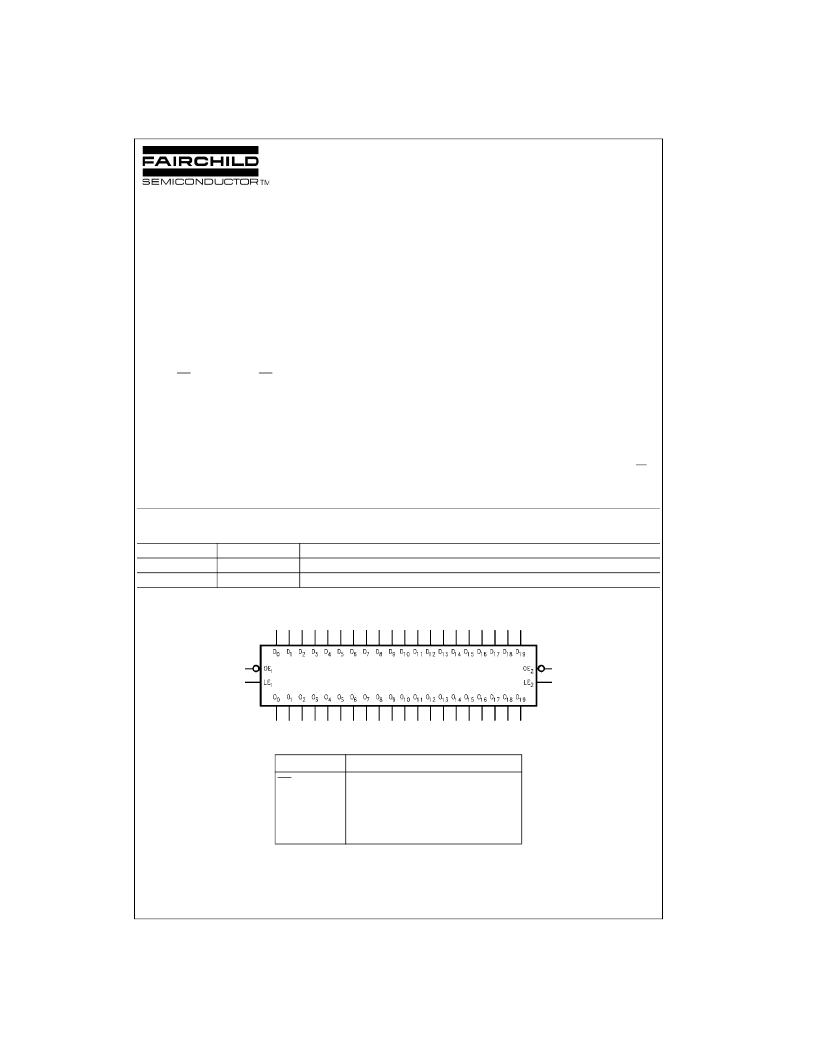

Logic Symbol

Pin Descriptions

Order Number

74LCX16841MEA

74LCX16841MTD

Package Number

MS56A

MTD56

Package Description

56-Lead Shrink Small Outline Package (SSOP), JEDEC MO-118, 0.300 Wide

56-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm Wide

Pin Names

Description

OE

n

LE

n

D

0

–

D

19

O

0

–

O

19

Output Enable Input (Active LOW)

Latch Enable Input

Inputs

Outputs

相關PDF資料 |

PDF描述 |

|---|---|

| 74LCX16841MTD | Low Voltage 20-Bit Transparent Latch with 5V Tolerant Inputs and Outputs |

| 74LCX16841MTDX | 10-Bit D-Type Latch |

| 74LCX2244BQ | Low Voltage Buffer/Line Driver with 5V Tolerant Inputs and Outputs with 26ohm Series Resistors in the Outputs |

| 74LCX2244 | Low Voltage Buffer/Line Driver with 5V Tolerant Inputs and Outputs with 26W Series Resistors in the Outputs |

| 74LCX2244MTC | Low Voltage Buffer/Line Driver with 5V Tolerant Inputs and Outputs with 26W Series Resistors in the Outputs |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| 74LCX16841MEA_Q | 功能描述:閉鎖 20-Bit Trans Latch RoHS:否 制造商:Micrel 電路數(shù)量:1 邏輯類型:CMOS 邏輯系列:TTL 極性:Non-Inverting 輸出線路數(shù)量:9 高電平輸出電流: 低電平輸出電流: 傳播延遲時間: 電源電壓-最大:12 V 電源電壓-最小:5 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:SOIC-16 封裝:Reel |

| 74LCX16841MEAX | 功能描述:閉鎖 20-Bit Trans Latch RoHS:否 制造商:Micrel 電路數(shù)量:1 邏輯類型:CMOS 邏輯系列:TTL 極性:Non-Inverting 輸出線路數(shù)量:9 高電平輸出電流: 低電平輸出電流: 傳播延遲時間: 電源電壓-最大:12 V 電源電壓-最小:5 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:SOIC-16 封裝:Reel |

| 74LCX16841MTD | 功能描述:閉鎖 20-Bit Trans Latch RoHS:否 制造商:Micrel 電路數(shù)量:1 邏輯類型:CMOS 邏輯系列:TTL 極性:Non-Inverting 輸出線路數(shù)量:9 高電平輸出電流: 低電平輸出電流: 傳播延遲時間: 電源電壓-最大:12 V 電源電壓-最小:5 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:SOIC-16 封裝:Reel |

| 74LCX16841MTD_Q | 功能描述:閉鎖 20-Bit Trans Latch RoHS:否 制造商:Micrel 電路數(shù)量:1 邏輯類型:CMOS 邏輯系列:TTL 極性:Non-Inverting 輸出線路數(shù)量:9 高電平輸出電流: 低電平輸出電流: 傳播延遲時間: 電源電壓-最大:12 V 電源電壓-最小:5 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:SOIC-16 封裝:Reel |

| 74LCX16841MTDX | 功能描述:閉鎖 20-Bit Trans Latch RoHS:否 制造商:Micrel 電路數(shù)量:1 邏輯類型:CMOS 邏輯系列:TTL 極性:Non-Inverting 輸出線路數(shù)量:9 高電平輸出電流: 低電平輸出電流: 傳播延遲時間: 電源電壓-最大:12 V 電源電壓-最小:5 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:SOIC-16 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復。