- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369288 > 74AC16862 (Texas Instruments, Inc.) 20-Bit Bus Transceivers With 3-State Outputs(20位總線收發(fā)器(三態(tài)輸出)) PDF資料下載

參數(shù)資料

| 型號(hào): | 74AC16862 |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | 20-Bit Bus Transceivers With 3-State Outputs(20位總線收發(fā)器(三態(tài)輸出)) |

| 中文描述: | 20位總線收發(fā)器與三態(tài)輸出(20位總線收發(fā)器(三態(tài)輸出)) |

| 文件頁(yè)數(shù): | 1/2頁(yè) |

| 文件大?。?/td> | 20K |

| 代理商: | 74AC16862 |

54AC16862, 54ACT16862

74AC16862, 74ACT16862

20-BIT BUS TRANSCEIVERS WITH 3-STATE OUTPUTS

SCAS411 – JUNE 1990

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

Copyright

1990, Texas Instruments Incorporated

1

PRODUCT PREVIEW information concerns products in

Characteristic data and other specifications are design

goals. Texas Instruments reserves the right to change or

discontinue these products without notice.

Members of Texas Instruments Widebus

Family

Packaged in Shrink Small-Outline 300-mil

Packages (SSOP) and 380-mil Fine-Pitch

Ceramic Flat Packages Using 25-mil

Center-to-Center Pin Spacings

Inputs are TTL- or CMOS-Voltage

Compatible

3-State Outputs Drive Bus Lines Directly

Flow-Through Architecture Optimizes PCB

Layout

Distributed V

CC

and GND Pin Configuration

Minimizes High-Speed Switching Noise

EPIC

(Enhanced-Performance Implanted

CMOS) 1-

μ

m Process

500-mA Typical Latch-Up Immunity at

125

°

C

description

The ’AC16862 and ’ACT16862 are inverting 20-bit

bus transceivers composed of two 10-bit

transceiver sections with separate control

signals. These devices allow data transmission

from the A bus to the B bus or from the B bus to the

A bus, depending upon the levels present at the

output-enable inputs (1GAB, 2GAB, 1GBA, and

2GBA). The control logic also allows for isolation

and latching.

The 74AC16862 and 74ACT16862 are packaged in TI’s shrink small-outline package (SSOP) with 25-mil

center-to-center pin spacings. This package provides twice the I/O pin count and functionality of a standard

small-outline package in the same printed-circuit-board area.

The ’AC16862 has CMOS-compatible input thresholds. The ’ACT16862 has TTL-compatible input thresholds.

The 54AC16862 and 54ACT16862 are characterized over the full military temperature range of –55

°

C to 125

°

C.

The 74AC16862 and 74ACT16862 are characterized for operation from –40

°

C to 85

°

C.

FUNCTION TABLE, EACH SECTION

INPUTS

GAB

GBA

L

H

H

L

H

H

L

L

OPERATION

A to B

B to A

Isolation

Latch A and B

(A = B)

EPIC and Widebus are trademarks of Texas Instruments

Incorporated.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

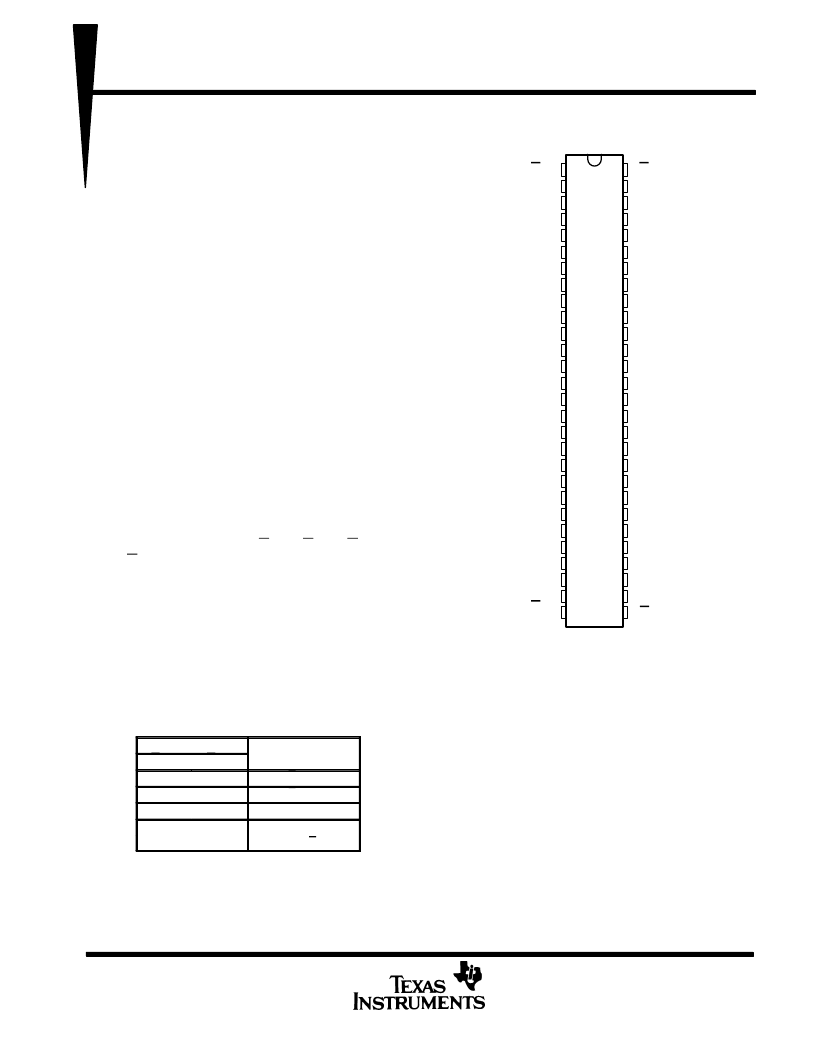

1GAB

1B1

1B2

GND

1B3

1B4

V

CC

1B5

1B6

1B7

GND

1B8

1B9

1B10

2B1

2B2

2B3

GND

2B4

2B5

2B6

V

CC

2B7

2B8

GND

2B9

2B10

1GBA

1A1

1A2

GND

1A3

1A4

V

CC

1A5

1A6

1A7

GND

1A8

1A9

1A10

2A1

2A2

2A3

GND

2A4

2A5

2A6

V

CC

2A7

2A8

GND

2A9

2A10

16862, 54ACT16862 . . . WD PACKAGE

16862, 74ACT16862 . . . DL PACKAGE

(T0P VIEW)

P

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 74ACT16862 | 20-Bit Bus Transceivers With 3-State Outputs(20位總線收發(fā)器(三態(tài)輸出)) |

| 74AC16953 | 16-Bit Registered Bus Transceivers With 3-State Outputs(16位記錄總線收發(fā)器(三態(tài)輸出)) |

| 74ACT16953 | 16-Bit Registered Bus Transceivers With 3-State Outputs(16位記錄總線收發(fā)器(三態(tài)輸出)) |

| 74AC174B | HEX D-TYPE FLIP FLOP WITH CLEAR |

| 74AC174M | HEX D-TYPE FLIP FLOP WITH CLEAR |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 74AC16862DL | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Logic IC |

| 74AC16863DL | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Logic IC |

| 74AC16864DL | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Logic IC |

| 74AC169 | 制造商:FAIRCHILD 制造商全稱:Fairchild Semiconductor 功能描述:4-Stage Synchronous Bidirectional Counter |

| 74AC169 WAF | 制造商:Fairchild Semiconductor Corporation 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。