- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄294128 > 72V805L15PF8 (INTEGRATED DEVICE TECHNOLOGY INC) 256 X 18 BI-DIRECTIONAL FIFO, 10 ns, PQFP128 PDF資料下載

參數(shù)資料

| 型號: | 72V805L15PF8 |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | FIFO |

| 英文描述: | 256 X 18 BI-DIRECTIONAL FIFO, 10 ns, PQFP128 |

| 封裝: | TQFP-128 |

| 文件頁數(shù): | 15/26頁 |

| 文件大?。?/td> | 325K |

| 代理商: | 72V805L15PF8 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁當(dāng)前第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁

22

IDT72V805/72V815/72V825/72V835/72V845

3.3 V CMOS DUAL SyncFIFO 256 x 18, 512 x 18, 1,024 x 18, 4,096 x 18

COMMERCIAL AND INDUSTRIAL

TEMPERATURE RANGES

NOTES:

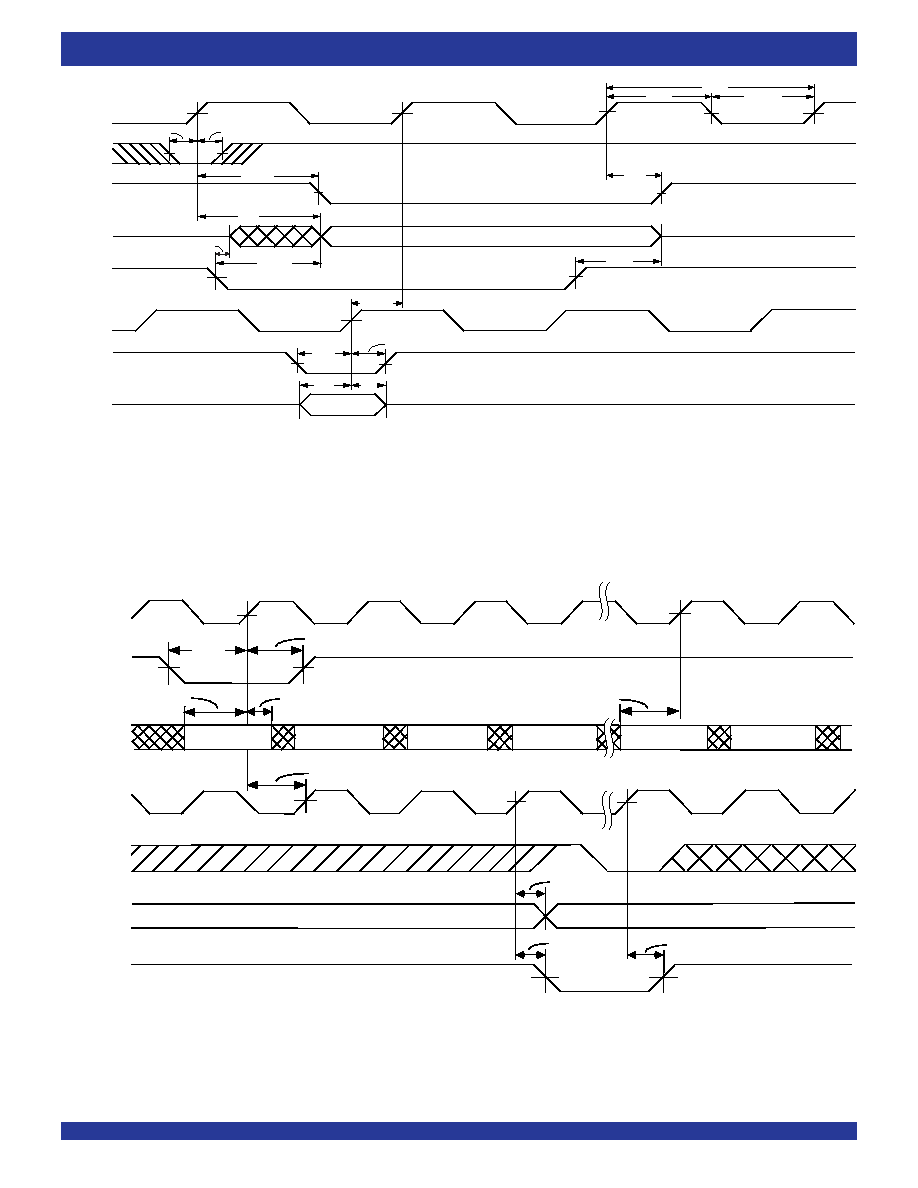

1. tSKEW1 is the minimum time between a rising WCLK edge and a rising RCLK edge to guarantee that

EF will go HIGH after one RCLK cycle plus tREF. If the time between the rising

edge of WCLK and the rising edge of RCLK is less than tSKEW1. then the

EF deassertion may be delayed an extra RCLK cycle.

2.

LD = HIGH

3. Select this mode by setting (

FL, RXI, WXI) = (0,1,0) or (1,1,0) during Reset.

Figure 26. Read Cycle Timing with Double Register-Buffered

EF (IDT Standard Timing)

NO OPERATION

RCLK

REN

EF

tCLKL

tENH

tREF

LAST WORD

tA

tOLZ

tOE

Q0 - Q17

OE

WCLK

(1)

WEN

4295 drw 26

D0 - D17

tENS

tENH

tDS

FIRST WORD

tOHZ

12

tCLK

tCLKH

tREF

tSKEW1

tDH

W1

W2

W4

W[n +2]

W[n+3]

WCLK

WEN

D0

- D17

RCLK

tDH

tDS

tSKEW1

REN

Q0

- Q17

tDS

tA

tREF

OR

W1

DATA IN OUTPUT REGISTER

(1)

W3

1

2

3

tENH

tREF

4295 drw 27

tENS

NOTES:

1. tSKEW1 is the minimum time between a rising WCLK edge and a rising RCLK edge for

OR to go HIGH during the current cycle. If the time between the rising edge of WLCK and the

rising edge of RCLK is less than tSKEW1, then the

OR deassertion may be delayed one extra RCLK cycle.

2.

LD = HIGH, OE = LOW

3. Select this mode by setting (

FL, RXI, WXI) = (0,0,1) or (1,0,1) during Reset.

Figure 27.

OR Flag Timing and First Word Fall Through when FIFO is Empty (FWFT mode)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 7305-0-15-15-47-14-04-0 | BRASS, GOLD FINISH, PCB TERMINAL |

| 7305-0-15-15-47-01-04-0 | BRASS, GOLD FINISH, PCB TERMINAL |

| 7305-0-15-01-47-27-04-0 | BRASS, TIN FINISH, PCB TERMINAL |

| 7305-0-15-01-47-14-04-0 | BRASS, TIN FINISH, PCB TERMINAL |

| 73068-T | FEMALE-MALE, RF STRAIGHT ADAPTER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 72V805L15PFI | 制造商:Integrated Device Technology Inc 功能描述:FIFO Mem Sync Quad Depth/Width Bi-Dir 256 x 18 x 2 128-Pin TQFP 制造商:Integrated Device Technology Inc 功能描述:FIFO SYNC QUAD DEPTH/WIDTH BI-DIR 256 X 18 X 2 128TQFP - Rail/Tube |

| 72V805L15PFI8 | 制造商:Integrated Device Technology Inc 功能描述:FIFO Mem Sync Quad Depth/Width Bi-Dir 256 x 18 x 2 128-Pin TQFP T/R 制造商:Integrated Device Technology Inc 功能描述:FIFO SYNC QUAD DEPTH/WIDTH BI-DIR 256 X 18 X 2 128TQFP - Tape and Reel |

| 72V805L20PF | 功能描述:先進(jìn)先出 RoHS:否 制造商:IDT 電路數(shù)量: 數(shù)據(jù)總線寬度:18 bit 總線定向:Unidirectional 存儲容量:4 Mbit 定時類型:Synchronous 組織:256 K x 18 最大時鐘頻率:100 MHz 訪問時間:10 ns 電源電壓-最大:3.6 V 電源電壓-最小:6 V 最大工作電流:35 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-80 封裝: |

| 72V805L20PF8 | 制造商:Integrated Device Technology Inc 功能描述:FIFO Mem Sync Quad Depth/Width Bi-Dir 256 x 18 x 2 128-Pin TQFP T/R 制造商:Integrated Device Technology Inc 功能描述:FIFO SYNC QUAD DEPTH/WIDTH BI-DIR 256 X 18 X 2 128TQFP - Tape and Reel |

| 72V811L10PF | 功能描述:先進(jìn)先出 RoHS:否 制造商:IDT 電路數(shù)量: 數(shù)據(jù)總線寬度:18 bit 總線定向:Unidirectional 存儲容量:4 Mbit 定時類型:Synchronous 組織:256 K x 18 最大時鐘頻率:100 MHz 訪問時間:10 ns 電源電壓-最大:3.6 V 電源電壓-最小:6 V 最大工作電流:35 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-80 封裝: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。