- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄360262 > 5962-8947702KYC AC/DC to Logic Interface Hermetically Sealed Optocouplers PDF資料下載

參數(shù)資料

| 型號(hào): | 5962-8947702KYC |

| 英文描述: | AC/DC to Logic Interface Hermetically Sealed Optocouplers |

| 中文描述: | AC / DC的邏輯接口氣密密封光電耦合器 |

| 文件頁(yè)數(shù): | 7/11頁(yè) |

| 文件大小: | 164K |

| 代理商: | 5962-8947702KYC |

7

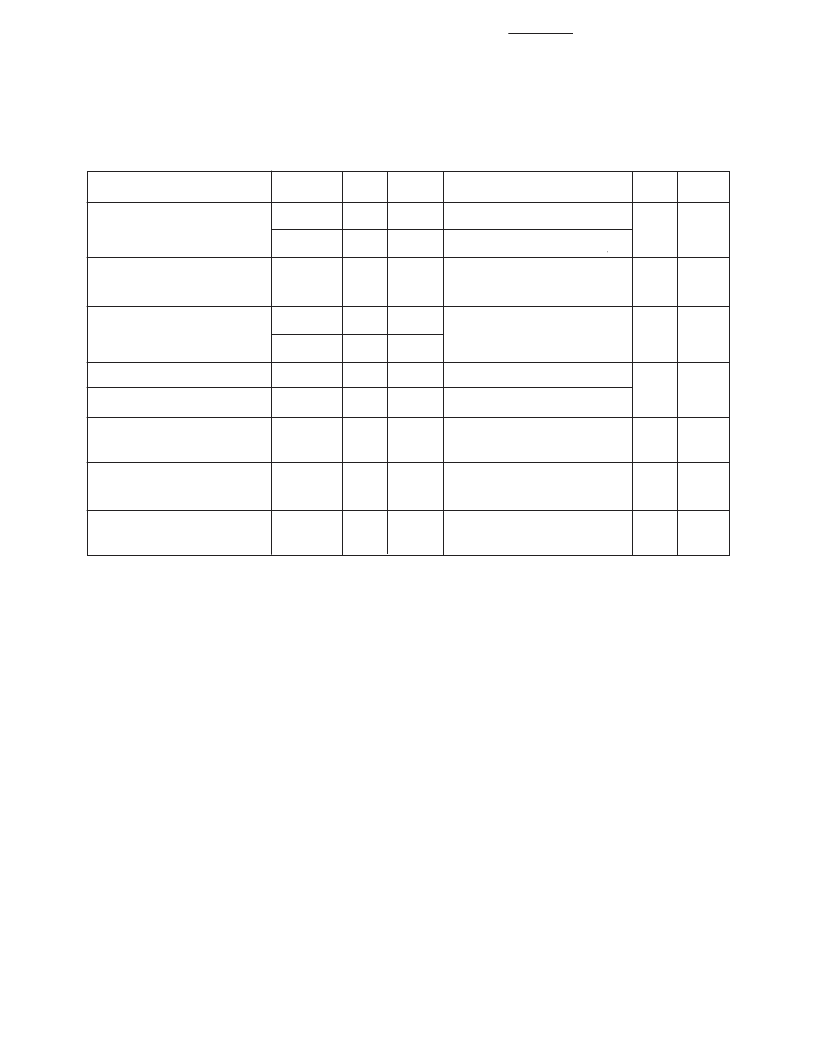

Parameter

Symbol

Typ.

Units

Conditions

Fig.

Note

I

HYS

1.2

mA

I

HYS

= I

TH+

- I

TH-

Hysteresis

1

V

HYS

1.1

V

V

HYS

= V

TH+

- V

TH-

Input Clamp Voltage

V

ILC

-0.76

V

V

ILC

= V

2

- V

3

; V

3

= GND;

I

IN

= -10 mA

Bridge Diode

Forward Voltage

V

D1,2

0.62

I

IN

= 3 mA (see schematic)

V

D3,4

R

I-O

0.73

Input-Output Resistance

10

12

V

I-O

= 500 Vdc

9

Input-Output Capacitance

C

I-O

2.0

pF

f = 1 MHz, V

I-O

= 0 Vdc

Input Capacitance

C

IN

50

pF

f = 1 MHz; V

IN

= 0 V,

Pins 2 & 3, Pins 1 & 4 Open

Output Rise Time

(10-90%)

t

r

10

μ

s

7

Output Fall Time

(90-10%)

t

f

0.5

μ

s

7

Typical Characteristics

All typical values are at T

A

= 25

°

C, V

CC

= 5 V, unless otherwise specified.

Notes:

1. Maximum operating frequency is

defined when output waveform (Pin 6)

attains only 90% of V

CC

with R

L

= 1.8

k

, C

L

= 15 pF using a 5 V square

wave input signal.

2. Measured at a point 1.6 mm below

seating plane.

3. Current into/out of any single lead.

4. Surge input current duration is 3 ms at

120 Hz pulse repetition rate. Transient

input current duration is 10

μ

s at

120 Hz pulse repetition rate. Note that

maximum input power, P

IN

, must be

observed.

5. Derate linearly above 100

°

C free-air

temperature at a rate of 4.26 mW/

°

C.

Maximum input power dissipation of

195 mW allows an input IC junction

temperature of 150

°

C at an ambient

temperature of T

A

= 125

°

C with a

typical thermal resistance from

junction to ambient of

θ

JA

= 235

°

C/W.

The typical thermal resistance from

junction to case is equal to 170

°

C/W.

Excessive P

IN

and T

J

may result in

device degradation.

6. The 1.8 k

load represents 1 TTL unit

load of 1.6 mA and the 4.7 k

pull-up

resistor.

7. Logic low output level at Pin 6 occurs

under the conditions of V

IN

≥

V

TH+

as

well as the range of V

IN

> V

TH

– once

V

IN

has exceeded V

TH+

. Logic high

output level at Pin 6 occurs under the

conditions of V

IN

≤

V

TH-

as well as the

range of V

IN

< V

TH+

once V

IN

has

decreased below V

TH-

.

8. The ac voltage is instantaneous

voltage.

9. Device considered a two terminal

device: Pins 1, 2, 3, 4 connected

together, Pins 5, 6, 7 8 connected

together.

10. This is a momentary withstand test,

not an operating condition.

11. The t

PHL

propagation delay is

measured from the 2.5 V level of the

leading edge of a 5.0 V input pulse (1

μ

s rise time) to the 1.5 V level on the

leading edge of the output pulse (see

Figure 7).

12. The t

PLH

propagation delay is

measured from the 2.5 V level of the

trailing edge of a 5.0 V input pulse (1

μ

s fall time) to the 1.5 V level on the

trailing edge of the output pulse (see

Figure 7).

13. Common mode transient immunity in

Logic High level is the maximum

tolerable dV

CM/dt

of the common mode

voltage, V

CM

, to ensure that the output

will remain in a Logic High state (i.e.,

V

O

> 2.0 V). Common mode transient

immunity in Logic Low level is the

maximum tolerable dV

CM/dt

of the

common mode voltage, V

CM

, to ensure

that the output will remain in a Logic

Low state (i.e., V

O

< 0.8 V). See

Figure 8.

14. In applications where dV

CM/dt

may

exceed 50,000 V/

μ

s (such as static

discharge), a series resistor, R

CC

,

should be included to protect the

detector IC from destructively high

surge currents. The recommended

value for R

CC

is 240

per volt of

allowable drop in V

CC

(between Pin 8

and V

CC

) with a minimum value of

240

.

15. D

1

and D

2

are Schottky diodes; D

3

and D

4

are zener diodes.

16. Standard parts receive 100% testing at

25

°

C (Subgroups 1 and 9). SMD,

Class H and Class K parts receive

100% testing at 25, 125, and -55

°

C

(Subgroups 1 and 9, 2 and 10 ,3 and

11, respectively.)

17. Parameters shall be tested as part of

device initial characterization and after

process changes. Parameters shall be

guaranteed to the limits specified for

all lots not specifically tested.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 5962-9583401Q2A | Line Receiver |

| 5962-9583401QFA | Line Receiver |

| 5962-9583501Q2X | Fast, Low-Voltage, 2.5 Ohm, SPST, CMOS Analog Switches |

| 5962-9583501QRX | 8-Bit D-Type Latch |

| 5962-9583501QSX | Fast, Low-Voltage, 2.5 Ohm, SPST, CMOS Analog Switches |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 5962-8947902GA | 制造商:Rochester Electronics LLC 功能描述:+10V REFERENCE IC - Bulk |

| 5962-89481012C | 功能描述:數(shù)模轉(zhuǎn)換器- DAC NULL RoHS:否 制造商:Texas Instruments 轉(zhuǎn)換器數(shù)量:1 DAC 輸出端數(shù)量:1 轉(zhuǎn)換速率:2 MSPs 分辨率:16 bit 接口類(lèi)型:QSPI, SPI, Serial (3-Wire, Microwire) 穩(wěn)定時(shí)間:1 us 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-14 封裝:Tube |

| 5962-8948101VA | 功能描述:數(shù)模轉(zhuǎn)換器- DAC RoHS:否 制造商:Texas Instruments 轉(zhuǎn)換器數(shù)量:1 DAC 輸出端數(shù)量:1 轉(zhuǎn)換速率:2 MSPs 分辨率:16 bit 接口類(lèi)型:QSPI, SPI, Serial (3-Wire, Microwire) 穩(wěn)定時(shí)間:1 us 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-14 封裝:Tube |

| 5962-89481022A | 制造商:Rochester Electronics LLC 功能描述: 制造商:Analog Devices 功能描述: |

| 5962-89481022C | 功能描述:數(shù)模轉(zhuǎn)換器- DAC RoHS:否 制造商:Texas Instruments 轉(zhuǎn)換器數(shù)量:1 DAC 輸出端數(shù)量:1 轉(zhuǎn)換速率:2 MSPs 分辨率:16 bit 接口類(lèi)型:QSPI, SPI, Serial (3-Wire, Microwire) 穩(wěn)定時(shí)間:1 us 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-14 封裝:Tube |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。