- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄156847 > 514JAAXXXXXXAAGR (SILICON LABORATORIES) 250 MHz, OTHER CLOCK GENERATOR, PDSO6 PDF資料下載

參數(shù)資料

| 型號(hào): | 514JAAXXXXXXAAGR |

| 廠商: | SILICON LABORATORIES |

| 元件分類: | 時(shí)鐘產(chǎn)生/分配 |

| 英文描述: | 250 MHz, OTHER CLOCK GENERATOR, PDSO6 |

| 封裝: | 5 X 7 MM, ROHS COMPILANT PACKAGE-6 |

| 文件頁(yè)數(shù): | 13/32頁(yè) |

| 文件大?。?/td> | 267K |

| 代理商: | 514JAAXXXXXXAAGR |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)當(dāng)前第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)

Si514

20

Preliminary Rev. 0.9

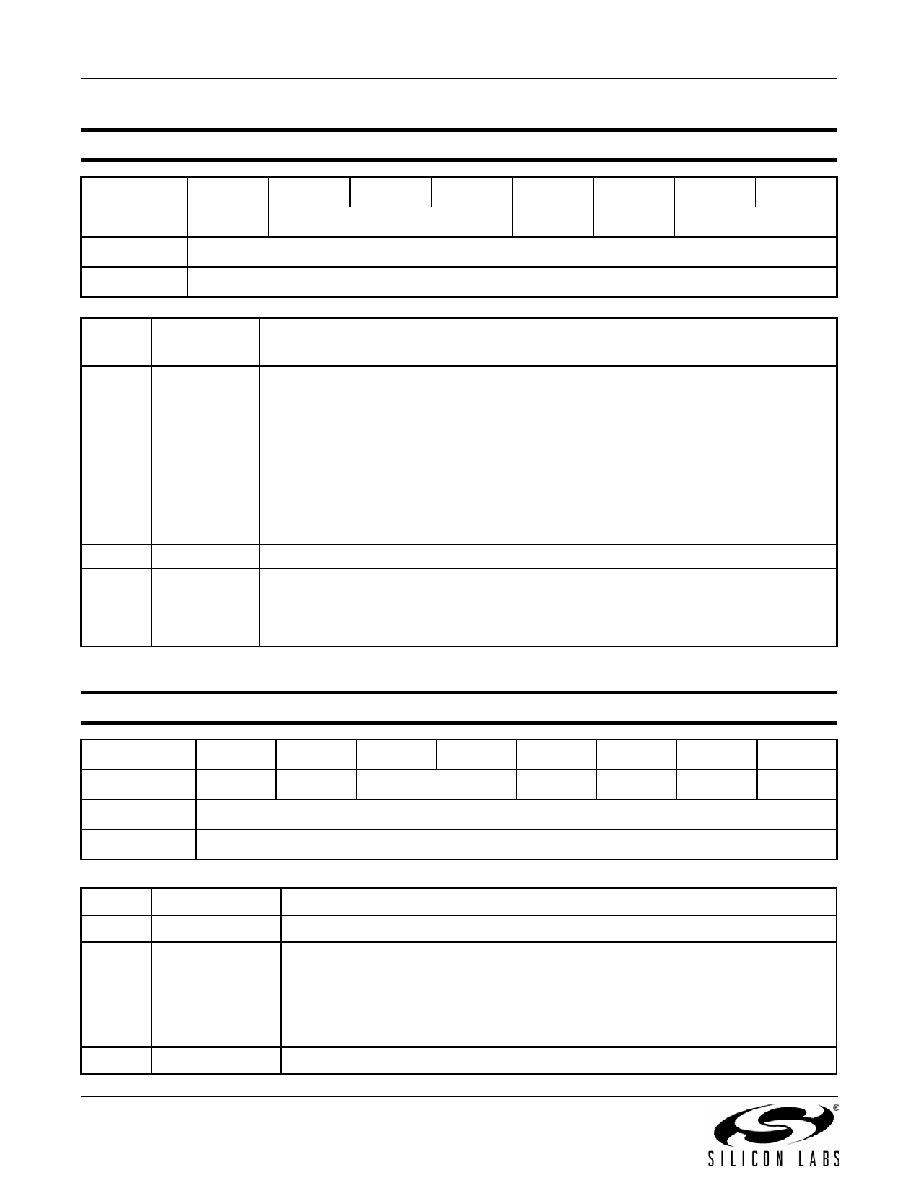

Register 11.

Bit

7654

3210

Name

LS_DIV[2:0]

HS_DIV[9:8]

Type

R/W

Default

Varies

Bit

Name

Function

7

Reserved

6:4

LS_DIV[2:0]

Last output divider stage. Used during large frequency changes. To update, follow

large frequency change procedure. LS_DIV value updates asynchronously.

000: divide-by-1

001: divide-by-2

010: divide-by-4

011: divide-by-8

100: divide-by-16

101: divide-by-32

All others reserved.

3:2

Reserved

1:0

HS_DIV[9:8]

Integer divider that divides VCO frequency and provides output to LS-DIV. Follow the

large frequency change procedure when updating. The allowed values are even num-

bers in the range from 10 to 1022 (i.e., 10, 12, 14, 16, ..., 1022). The decimal value

represents the actual divide value (i.e., 12 means divide-by-12).

Register 14.

Bit

7

65

43

2

1

0

Name

OE_STATE[1:0]

Type

R/W

Default

0

Bit

Name

Function

7:6

Reserved

5:4

OE_STATE[1:0]

Sets logic state of output when output disabled.

00: high impedance

10: logic low when output disabled

01: logic high when output disabled

11: reserved

3:0

Reserved

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 514JAAXXXXXXBAGR | 250 MHz, OTHER CLOCK GENERATOR, PDSO6 |

| 514JABXXXXXXBAGR | 170 MHz, OTHER CLOCK GENERATOR, PDSO6 |

| 514JACXXXXXXAAG | 125 MHz, OTHER CLOCK GENERATOR, PDSO6 |

| 514JBAXXXXXXAAG | 250 MHz, OTHER CLOCK GENERATOR, PDSO6 |

| 514JBCXXXXXXAAG | 125 MHz, OTHER CLOCK GENERATOR, PDSO6 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 514JBB001011BAG | 制造商:Silicon Laboratories Inc 功能描述:OSCILLATOR - Trays |

| 514JCA000269BAG | 制造商:Silicon Laboratories Inc 功能描述:OSCILLATOR - Trays |

| 514JCA001267BAG | 制造商:Silicon Laboratories Inc 功能描述:OSCILLATOR - Trays |

| 514JCB000159BAG | 制造商:Silicon Laboratories Inc 功能描述:OSCILLATOR - Trays |

| 514JCB000159BAGR | 制造商:Silicon Laboratories Inc 功能描述:OSCILLATOR - Tape and Reel |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。