- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359863 > 4022B 300mA LDO Linear Regulators with Internal Microprocessor Reset Circuit PDF資料下載

參數(shù)資料

| 型號: | 4022B |

| 元件分類: | 復位半導體 |

| 英文描述: | 300mA LDO Linear Regulators with Internal Microprocessor Reset Circuit |

| 中文描述: | (280.26十一) |

| 文件頁數(shù): | 1/12頁 |

| 文件大小: | 280K |

| 代理商: | 4022B |

HCC/HCF4017B

HCC/HCF4022B

COUNTERS/DIVIDERS

FULLY STATIC OPERATION

.

MEDIUMSPEEDOPERATION-12MHz (typ.)AT

V

DD

= 10V

.

STANDARDIZED

CHARACTERISTICS

.

QUIESCENT CURRENT SPECIFIED TO 20V

FOR HCC DEVICE

.

INPUT CURRENTOF100nA AT18V AND 25

°

C

FOR HCC DEVICE

.

100% TESTEDFOR QUIESCENTCURRENT

.

5V, 10V, AND 15V PARAMETRIC RATINGS

.

MEETSALLREQUIREMENTSOFJEDECTEN-

TATIVE STANDARD N

°

13A, ”STANDARD

SPECIFICATIONS FOR DESCRIPTION OF ”B”

SERIESCMOS DEVICES”

SYMMETRICAL

OUTPUT

June 1989

EY

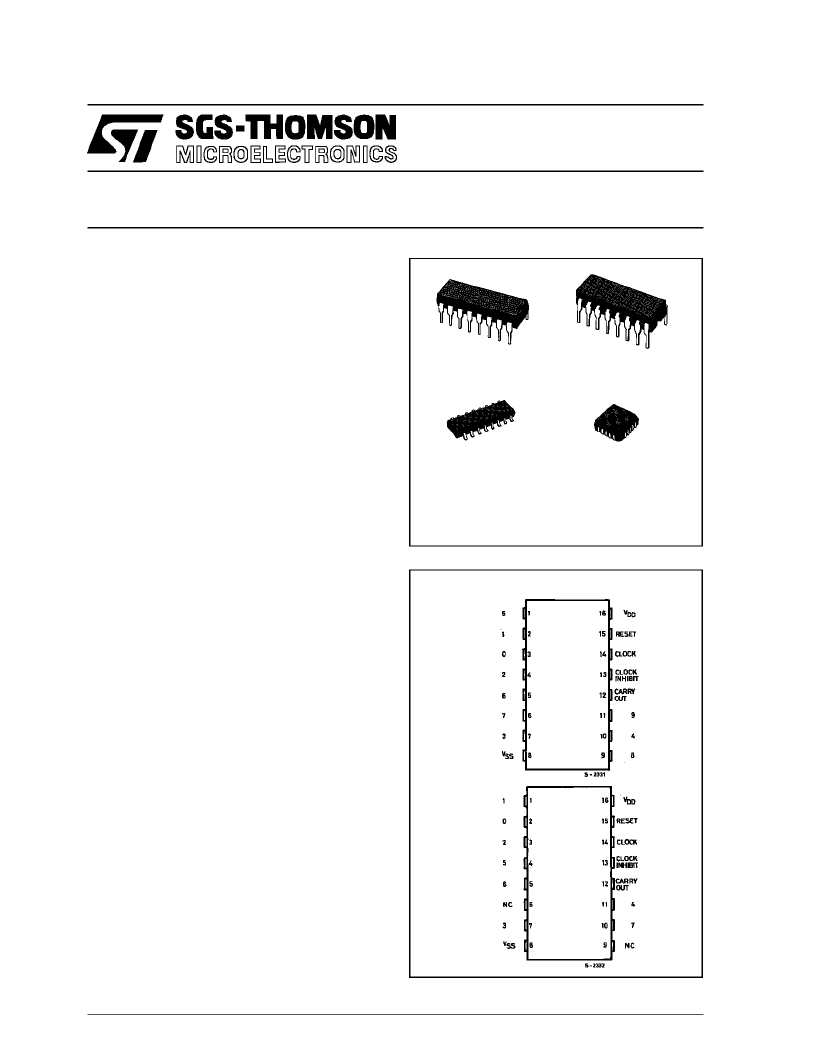

(Plastic Package)

F

(Ceramic Frit Seal Package)

C1

(Plastic Chip Carrier)

ORDERCODES :

HCC40XXBF

HCF40XXBEY

HCF40XXBM1

HCF40XXBC1

PIN CONNECTIONS

4017B DECADE COUNTER WITH 10

DECODED OUTPUTS

4022B OCTAL COUNTER WITH 8

DECODED OUTPUTS

4017B

4022B

M1

(Micro Package)

DESCRIPTION

The

HCC4017B/4022B

(extended temperature

range) and

HCF4017B/4022B

(intermediate tem-

perature range) are monolithic integrated circuits,

available in 16-lead dual in-line plastic or ceramic

package and plastic micro package.

The

HCC/HCF4017B

and

HCC/HCF4022

B are 5-

stage and 4-stage Johnson counters having 10 and

8 decoded outputs, respectively. Inputs include a

CLOCK, a RESET, and a CLOCK INHIBIT signal.

SchmitttriggeractionintheCLOCKinputcircuit pro-

videspulse shapingthatallows unlimited clockinput

pulse rise and fall times. These counters are ad-

vanced one count at the positive clock signal tran-

sition if the CLOCK INHIBIT signal is low. Counter

advancement via the clock line is inhibited when the

CLOCKINHIBITsignalishigh.Ahigh RESET signal

clears the counter to its zero count. Use of the

Johnson

decade-counter

high-speed operation, 2-input decimal-decode gat-

ing, and spike-free decoded outputs. Anti-lock gat-

ing is provided, thus assuring proper counting

sequence. The decoded outputs are normally low

and go high only at their respective decoded time

slot. Each decoded output remains high for one full

clock cycle. A CARRY-OUT signal completes one

configuration

permits

1/12

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 401B2 | 300mA LDO Linear Regulators with Internal Microprocessor Reset Circuit |

| 401C2 | 300mA LDO Linear Regulators with Internal Microprocessor Reset Circuit |

| 401D2 | 300mA LDO Linear Regulators with Internal Microprocessor Reset Circuit |

| 401F2 | 300mA LDO Linear Regulators with Internal Microprocessor Reset Circuit |

| 401G | 300mA LDO Linear Regulators with Internal Microprocessor Reset Circuit |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 4022-B | 制造商:Brady Corporation 功能描述: |

| 4022BDC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| 4022BDCQR | 制造商:Texas Instruments 功能描述: |

| 4022BDM | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| 4022BE | 制造商:SSS 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復。