- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372303 > ST52F514Y0M6 IC MAX 7000 CPLD 64 44-TQFP PDF資料下載

參數(shù)資料

| 型號: | ST52F514Y0M6 |

| 英文描述: | IC MAX 7000 CPLD 64 44-TQFP |

| 中文描述: | 微控制器 |

| 文件頁數(shù): | 30/106頁 |

| 文件大小: | 648K |

| 代理商: | ST52F514Y0M6 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁當(dāng)前第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁

ST52F510/F513/F514

30/106

4 MEMORY PROGRAMMING

ST52F510/F513/F514 provides an on-chip user

programmable non-volatile memory, which allows

fast and reliable storage of user data.

Program/Data

Memory

composed by a Single Voltage Flash Memory and

a RAM memory bench. The

devices also have a Data EEPROM benchto store

permanent data with longterm retention anda high

number of write/erase cycles.

All the Program Data memory addresses can

execute code, including RAM and EEPROM

benches.

The memory is programmed by setting the V

pp

pin

equal to V

dd

. Data and commands are transmitted

through the I

2

C serial communicationprotocol. The

same procedure is used to perform “In-Situ” the

programming of the device after it is mounted in

the user system. Data can also be written in run-

time with the In-Application Programming (IAP).

The Memory can be locked by the user during the

programming phase, in order to prevent external

operation such as reading the program code and

assuring protection of user intellectual property.

Flash and EEPROM pages can be protected by

unintentional writings.

addressing

space

is

ST52F513/514

4.1 Program/Data Memory Organization

The Program/Data Memory is organized as

described in Section 3.3. The various sales types

have different amounts of each type of memory.

Table 4.1 describes the memory benches amount

and page allocation for each sales type.

Remark:

some devices have RAM or EEPROM

memory benches of 128 bytes. The address range

inside the page of these benches is between 128

to 255.

The addressing spaces are organized in pages of

256 bytes. Each page is composed by blocks of 32

bytes. Memory programming is performed one

block at a time in order

programming time (about 2.5 ms per block).

The whole location address is composed as

follows:

to speed-up the

15

8

7

5

4

0

Pageaddress

Block address address insidethe block

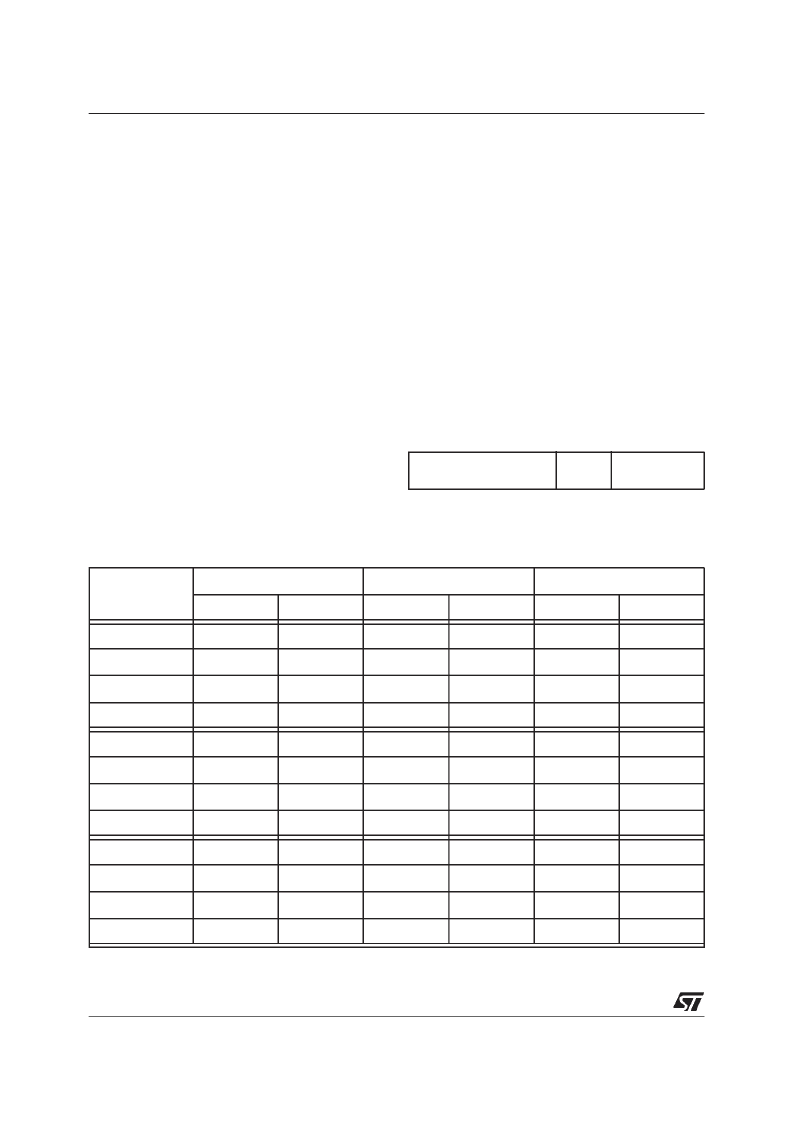

Table 4.1 Sales Type Memory Organization

Device

Flash Memory

RAM Memory

EEPROM Memory

Amount

Pages

Amount

Page

Amount

Page(s)

ST52F510x0xx

1024 bytes

0 to 3

128 bytes

32*

-

-

ST52F510x1xx

2048 bytes

0 to 7

128 bytes

32*

-

-

ST52F510x2xx

4096 bytes

0 to 15

256 bytes

32

-

-

ST52F510x3xx

8192 bytes

0 to 31

256 bytes

32

-

-

ST52F513x0xx

896 bytes

0 to 3

128 bytes

32*

128 bytes

3*

ST52F513x1xx

1920 bytes

0 to 7

128 bytes

32*

128 bytes

7*

ST52F513x2xx

3840 bytes

0 to 14

256 bytes

32

256 bytes

15

ST52F513x3xx

7936 bytes

0 to 30

256 bytes

32

256 bytes

31

ST52F514x0xx

4096 bytes

0 to 15

256 bytes

32

512 bytes

16-17

ST52F514x1xx

4096 bytes

0 to 15

256 bytes

32

1024 bytes

16-19

ST52F514x2xx

4096 bytes

0 to 15

256 bytes

32

2048 bytes

16-23

ST52F514x3xx

4096 bytes

0 to 15

256 bytes

32

4096 bytes

16-31

(*) Addresses range from 128 to 255 inside the page

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ST52F514Y1B6 | MAX II CPLD 240 LE 100-TQFP |

| ST52F514Y1M6 | IC MAX 7000 CPLD 256 256-FBGA |

| ST52F514Y3B6 | IC MAX 7000 CPLD 128 144-TQFP |

| ST52F514Y3M6 | IC MAX 7000 CPLD 256 144-TQFP |

| ST5R33 | Programmable Logic IC; Logic Type:Programmable; No. of Macrocells:102; Package/Case:144-TQFP; Leaded Process Compatible:No; Number of Circuits:1728; Peak Reflow Compatible (260 C):No; Mounting Type:surface mount RoHS Compliant: No |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ST52F514Y1B6 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microcontroller |

| ST52F514Y1M6 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microcontroller |

| ST52F514Y3B6 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microcontroller |

| ST52F514Y3M6 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microcontroller |

| ST52F514YMM6 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:8-BIT INTELLIGENT CONTROLLER UNIT ICU Two Timer/PWMs, ADC, I2C, SPI, SCI |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。