- 您現(xiàn)在的位置:買賣IC網 > PDF目錄372303 > ST52F514F1B6 IC MAX 7000 CPLD 160 100-TQFP PDF資料下載

參數(shù)資料

| 型號: | ST52F514F1B6 |

| 英文描述: | IC MAX 7000 CPLD 160 100-TQFP |

| 中文描述: | 微控制器 |

| 文件頁數(shù): | 22/106頁 |

| 文件大?。?/td> | 648K |

| 代理商: | ST52F514F1B6 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁當前第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁

ST52F510/F513/F514

22/106

Flash and EEPROM are programmed electrically

just applying the supply voltage (2.4V to 5.5V)and

it is also erased electrically; this feature allows the

user to easily reprogram the memory without

taking the device off from the board (In Situ

Programming ISP). Data and commands are

transmitted through the I

2

C serial communication

protocol. Data can also be written run-time with the

In Application Programming (IAP)

NVM can be locked by the user during the

programming phase, in order to prevent external

operation such as reading the program code and

assuring protection of user intellectual property.

Flash and EEPROM pages can be protected by

unintentional writings.

The operations that can beperformed onthe NVM

during the Programming Phase, ISP and IAP are

described in detail in the Section 4.

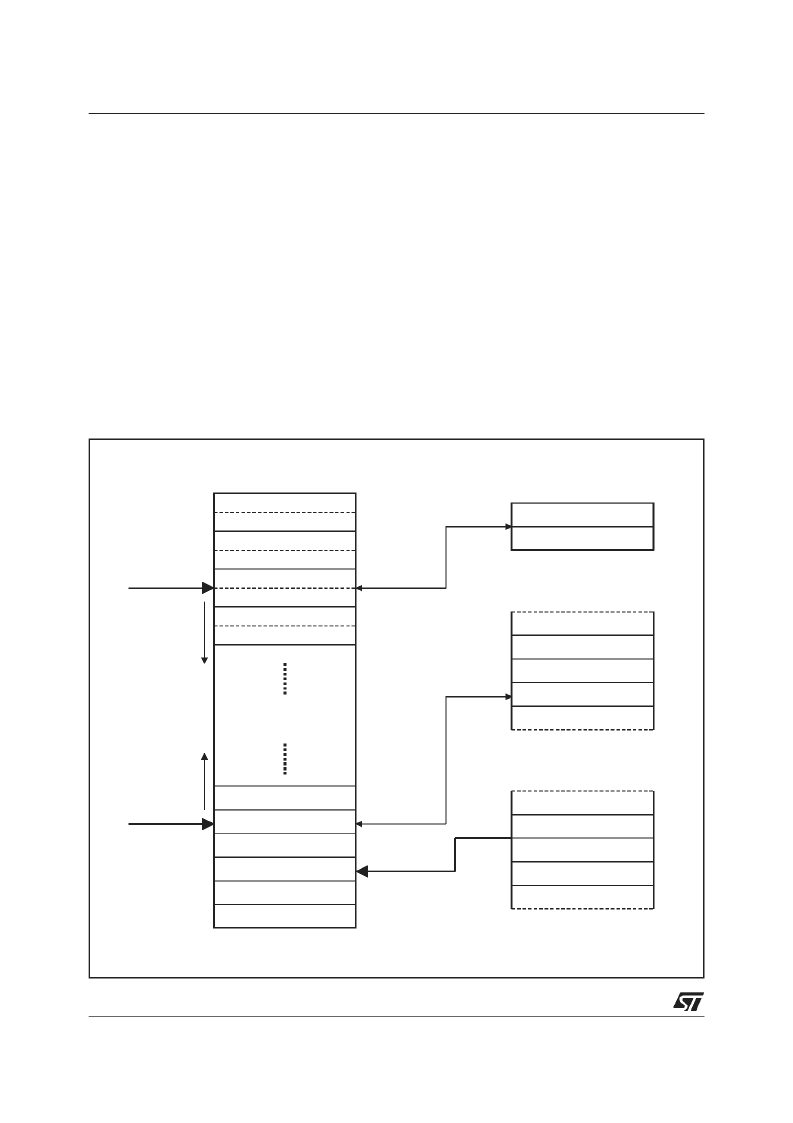

Figure 3.3 System and User Stack

3.4 System and User Stacks

The System and User Stacks are located in the

Program/Data memory in the RAM benches.

System Stacks are used to push the Program

Counter (PC) after an Interrupt Request or a

Subroutine Call. After a RET (Return from a

subroutine) or a RETI (Return from an interrupt)

the PC that is saved is popped from the stack and

restored. After an interrupt request, the flags are

also saved in a reserved stack inside the core, so

each interrupt has its own flags.

The System Stackis located in the last RAM bench

starting from the last address (255) inside the

bench page. The System Stack Pointer (SSP) can

be read and modified by the user. For each level of

stack 2 bytes of the RAMare used. The SSP points

to the first currently available stack position. When

a subroutine call or interrupt request occurs, the

content of the PC is stored in a couple of locations

pointed to by the SSP that is decreased by 2.

20FFh

2000h

2001h

20FEh

REGISTER FILE

CONFIGURATION REGISTERS

USER STACK TOP MSB

USER STACK TOP LSB

PROGRAM COUNTER

RAM BENCH

SYSTEM STACK

POINTER

USER STACK

POINTER

USER DATA

PAGE NUMBER

LOCATION ADRESS

IRQ

RETI

POP X

PUSH X

REGISTER X

LSB

MSB

SYSTEM STACK

SYSTEM STACK

SYSTEM STACK

SYSTEM STACK

LEVEL 1

LEVEL 2

LEVEL 3

LEVEL 4

USER STACK LEVEL 1

USER STACK LEVEL 2

USER STACK LEVEL 3

USER STACK LEVEL 4

相關PDF資料 |

PDF描述 |

|---|---|

| ST52F514F1M6 | IC MAX 7000 CPLD 256 208-PQFP |

| ST52F514F3B6 | IC MAX 7000 CPLD 256 208-PQFP |

| ST52F514F3M6 | IC MAX 7000 CPLD 256 256-FBGA |

| ST52F514G0B6 | IC MAX 7000 CPLD 256 256-FBGA |

| ST52F514G0M6 | IC MAX 7000 CPLD 64 100-TQFP |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| ST52F514F1M6 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microcontroller |

| ST52F514F3B6 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microcontroller |

| ST52F514F3M6 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microcontroller |

| ST52F514FMB6 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:8-BIT INTELLIGENT CONTROLLER UNIT ICU Two Timer/PWMs, ADC, I2C, SPI, SCI |

| ST52F514FMM6 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:8-BIT INTELLIGENT CONTROLLER UNIT ICU Two Timer/PWMs, ADC, I2C, SPI, SCI |

發(fā)布緊急采購,3分鐘左右您將得到回復。