- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374858 > SN74LVTH646DGV (Texas Instruments, Inc.) 3.3-V ABT OCTAL BUS TRANSCEIVERS AND REGISTERS WITH 3-STATE OUTPUTS PDF資料下載

參數(shù)資料

| 型號(hào): | SN74LVTH646DGV |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | 3.3-V ABT OCTAL BUS TRANSCEIVERS AND REGISTERS WITH 3-STATE OUTPUTS |

| 中文描述: | 的3.3V ABT生根粉八路總線收發(fā)器和3冊(cè)態(tài)輸出 |

| 文件頁(yè)數(shù): | 1/10頁(yè) |

| 文件大小: | 137K |

| 代理商: | SN74LVTH646DGV |

SN54LVTH646, SN74LVTH646

3.3-V ABT OCTAL BUS TRANSCEIVERS AND REGISTERS

WITH 3-STATE OUTPUTS

SCBS705E – AUGUST 1997 – REVISED APRIL 1999

1

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

State-of-the-Art Advanced BiCMOS

Technology (ABT) Design for 3.3-V

Operation and Low Static-Power

Dissipation

I

off

and Power-Up 3-State Support Hot

Insertion

Bus Hold on Data Inputs Eliminates the

Need for External Pullup/Pulldown

Resistors

Support Mixed-Mode Signal Operation

(5-V Input and Output Voltages With

3.3-V V

CC

)

Support Unregulated Battery Operation

Down to 2.7 V

Typical V

OLP

(Output Ground Bounce)

< 0.8 V at V

CC

= 3.3 V, T

A

= 25

°

C

Latch-Up Performance Exceeds 500 mA Per

JESD 17

ESD Protection Exceeds 2000 V Per

MIL-STD-883, Method 3015; Exceeds 200 V

Using Machine Model (C = 200 pF, R = 0)

Package Options Include Plastic

Small-Outline (DW), Shrink Small-Outline

(DB), Thin Shrink Small-Outline (PW), and

Thin Very Small-Outline (DGV) Packages,

Ceramic Chip Carriers (FK), Ceramic Flat

(W) Package, and Ceramic (JT) DIPs

description

These bus transceivers and registers are

designed specifically for low-voltage (3.3-V) V

CC

operation, but with the capability to provide a TTL

interface to a 5-V system environment.

The ’LVTH646 devices consist of bus transceiver circuits, D-type flip-flops, and control circuitry arranged for

multiplexed transmission of data directly from the input bus or from the internal registers. Data on the A or B

bus is clocked into the registers on the low-to-high transition of the appropriate clock (CLKAB or CLKBA) input.

Figure 1 illustrates the four fundamental bus-management functions that can be performed with the ’LVTH646.

Output-enable (OE) and direction-control (DIR) inputs are provided to control the transceiver functions. In the

transceiver mode, data present at the high-impedance port can be stored in either register or in both.

The select-control (SAB and SBA) inputs can multiplex stored and real-time (transparent mode) data. The

direction control (DIR) determines which bus receives data when OE is low. In the isolation mode (OE high),

A data can be stored in one register and/or B data can be stored in the other register.

Copyright

1999, Texas Instruments Incorporated

On products compliant to MIL-PRF-38535, all parameters are tested

unless otherwise noted. On all other products, production

processing does not necessarily include testing of all parameters.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

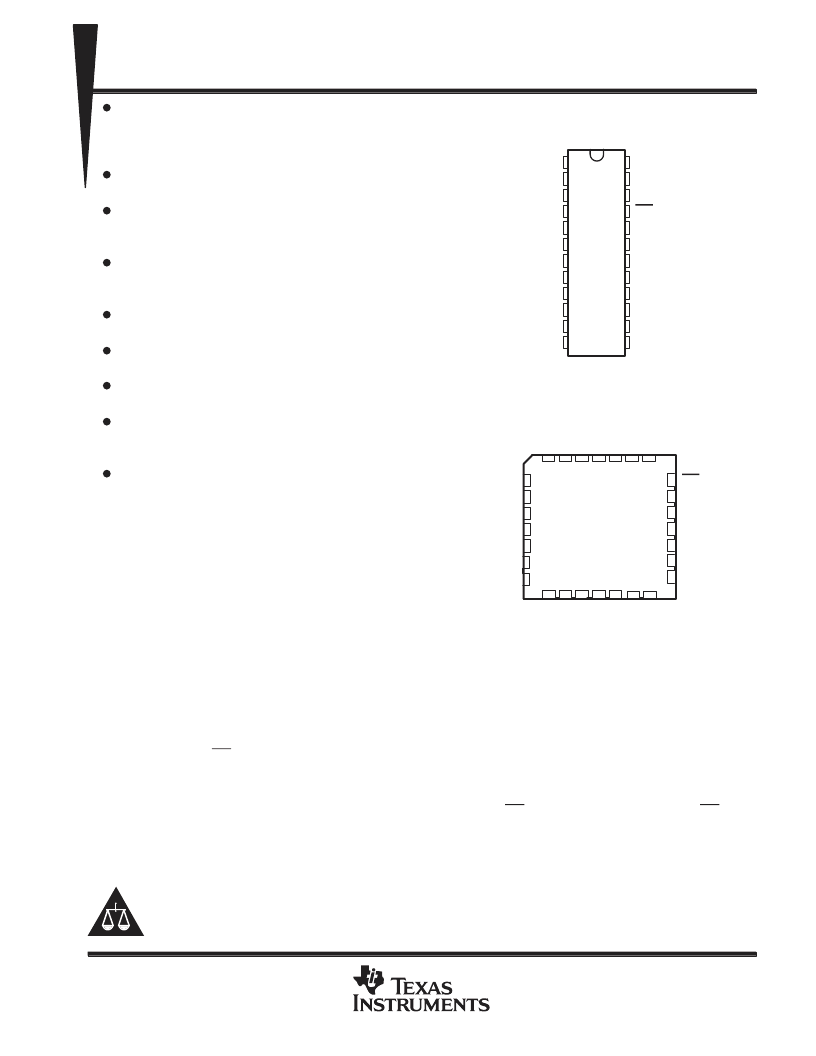

SN54LVTH646 . . . JT OR W PACKAGE

SN74LVTH646 . . . DB, DGV, DW, OR PW PACKAGE

(TOP VIEW)

SN54LVTH646 . . . FK PACKAGE

(TOP VIEW)

5

6

7

8

9

10

11

25

24

23

22

21

20

19

4

3

2 1 28

12 13 14 15 16

OE

B1

B2

NC

B3

B4

B5

A1

A2

A3

NC

A4

A5

A6

D

S

C

B

B

A

G

N

N

C

S

V

A

B

17 18

27 26

C

NC – No internal connection

CLKAB

SAB

DIR

A1

A2

A3

A4

A5

A6

A7

A8

GND

V

CC

CLKBA

SBA

OE

B1

B2

B3

B4

B5

B6

B7

B8

1

2

3

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SN54LVU04A | HEX INVERTERS |

| SN54LVU04AFK | Quad 2-Input Exclusive OR Gate; Package: SOIC 14 LEAD; No of Pins: 14; Container: Rail; Qty per Container: 55 |

| SN54LVU04AJ | Quad 2-Input Exclusive OR Gate; Package: SOIC 14 LEAD; No of Pins: 14; Container: Tape and Reel; Qty per Container: 2500 |

| SN54LVU04AW | Quad 2-Input Exclusive OR Gate; Package: SOIC 14 LEAD; No of Pins: 14; Container: Tape and Reel; Qty per Container: 2500 |

| SN55152 | DUAL LINE RECEIVERS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SN74LVTH646DGVR | 功能描述:總線收發(fā)器 Tri-St ABT Octal Bus RoHS:否 制造商:Fairchild Semiconductor 邏輯類型:CMOS 邏輯系列:74VCX 每芯片的通道數(shù)量:16 輸入電平:CMOS 輸出電平:CMOS 輸出類型:3-State 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時(shí)間:6.2 ns 電源電壓-最大:2.7 V, 3.6 V 電源電壓-最小:1.65 V, 2.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

| SN74LVTH646DGVRE4 | 功能描述:總線收發(fā)器 Single-Supply Voltage Translator RoHS:否 制造商:Fairchild Semiconductor 邏輯類型:CMOS 邏輯系列:74VCX 每芯片的通道數(shù)量:16 輸入電平:CMOS 輸出電平:CMOS 輸出類型:3-State 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時(shí)間:6.2 ns 電源電壓-最大:2.7 V, 3.6 V 電源電壓-最小:1.65 V, 2.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

| SN74LVTH646DGVRG4 | 功能描述:總線收發(fā)器 3.3V ABT Octal Bus Transceivr Registr RoHS:否 制造商:Fairchild Semiconductor 邏輯類型:CMOS 邏輯系列:74VCX 每芯片的通道數(shù)量:16 輸入電平:CMOS 輸出電平:CMOS 輸出類型:3-State 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時(shí)間:6.2 ns 電源電壓-最大:2.7 V, 3.6 V 電源電壓-最小:1.65 V, 2.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

| SN74LVTH646DW | 功能描述:總線收發(fā)器 Tri-St ABT Octal Bus RoHS:否 制造商:Fairchild Semiconductor 邏輯類型:CMOS 邏輯系列:74VCX 每芯片的通道數(shù)量:16 輸入電平:CMOS 輸出電平:CMOS 輸出類型:3-State 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時(shí)間:6.2 ns 電源電壓-最大:2.7 V, 3.6 V 電源電壓-最小:1.65 V, 2.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

| SN74LVTH646DWE4 | 功能描述:總線收發(fā)器 3.3V ABT Octal Bus Xcvr/Reg RoHS:否 制造商:Fairchild Semiconductor 邏輯類型:CMOS 邏輯系列:74VCX 每芯片的通道數(shù)量:16 輸入電平:CMOS 輸出電平:CMOS 輸出類型:3-State 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時(shí)間:6.2 ns 電源電壓-最大:2.7 V, 3.6 V 電源電壓-最小:1.65 V, 2.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。