-

[北京]010-87982920

-

[深圳]0755-82701186

- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374866 > SN74GTLPH16945KR (Texas Instruments, Inc.) 16-BIT LVTTL-TO-GTLP BUS TRANSCEIVER PDF資料下載

參數(shù)資料

| 型號: | SN74GTLPH16945KR |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | 16-BIT LVTTL-TO-GTLP BUS TRANSCEIVER |

| 中文描述: | 16位LVTTL至GTLP總線收發(fā)器 |

| 文件頁數(shù): | 1/13頁 |

| 文件大小: | 212K |

| 代理商: | SN74GTLPH16945KR |

SN74GTLPH16945

16-BIT LVTTL-TO-GTLP BUS TRANSCEIVER

SCES292D – OCTOBER 1999 – REVISED NOVEMBER 2001

1

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

Member of the Texas Instruments

Widebus

Family

TI-OPC

Circuitry Limits Ringing on

Unevenly Loaded Backplanes

OEC

Circuitry Improves Signal Integrity

and Reduces Electromagnetic Interference

Bidirectional Interface Between GTLP

Signal Levels and LVTTL Logic Levels

LVTTL Interfaces Are 5-V Tolerant

Medium-Drive GTLP Outputs (50 mA)

LVTTL Outputs (–24 mA/24 mA)

GTLP Rise and Fall Times Designed for

Optimal Data-Transfer Rate and Signal

Integrity in Distributed Loads

I

off

, Power-Up 3-State, and BIAS V

CC

Support Live Insertion

Bus Hold on A-Port Data Inputs

Distributed V

CC

and GND Pins Minimize

High-Speed Switching Noise

Latch-Up Performance Exceeds 100 mA Per

JESD 78, Class II

description

The SN74GTLPH16945 is a medium-drive, 16-bit

bus transceiver that provides LVTTL-to-GTLP and

GTLP-to-LVTTL signal-level translation. It is

partitioned as two 8-bit transceivers. The device

provides a high-speed interface between cards

operating at LVTTL logic levels and a backplane operating at GTLP signal levels. High-speed (about three times

faster than standard TTL or LVTTL) backplane operation is a direct result of GTLP’s reduced output swing

(<1 V), reduced input threshold levels, improved differential input, OEC

circuitry, and TI-OPC

circuitry.

Improved GTLP OEC and TI-OPC circuits minimize bus-settling time and have been designed and tested using

several backplane models. The medium drive allows incident-wave switching in heavily loaded backplanes with

equivalent load impedance down to 19

.

GTLP is the Texas Instruments derivative of the Gunning Transceiver Logic (GTL) JEDEC standard JESD 8-3.

The ac specification of the SN74GTLPH16945 is given only at the preferred higher noise margin GTLP, but the

user has the flexibility of using this device at either GTL (V

TT

= 1.2 V and V

REF

= 0.8 V) or GTLP (V

TT

= 1.5 V

and V

REF

= 1 V) signal levels.

Normally, the B port operates at GTLP signal levels. The A-port and control inputs operate at LVTTL logic levels

but are 5-V tolerant and are compatible with TTL and 5-V CMOS inputs. V

REF

is the B-port differential input

reference voltage.

Copyright

2001, Texas Instruments Incorporated

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

OEC, TI-OPC, and Widebus are trademarks of Texas Instruments.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

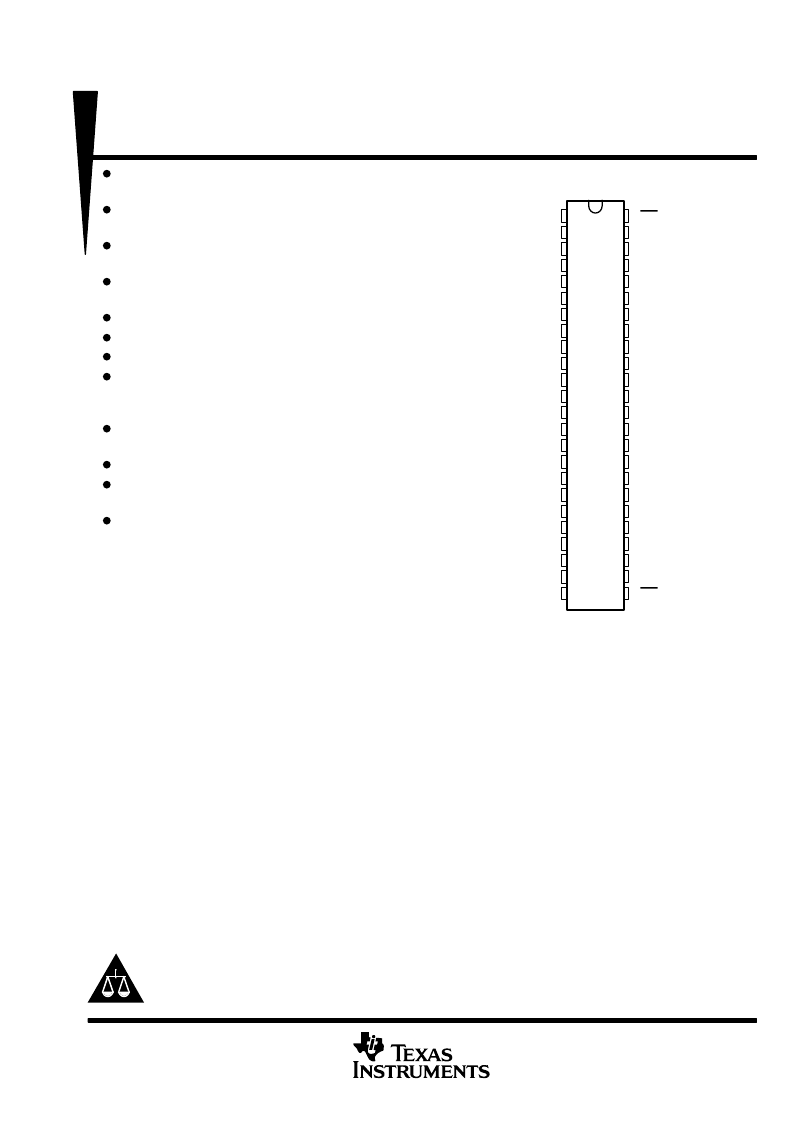

DGG OR DGV PACKAGE

(TOP VIEW)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

1DIR

1A1

1A2

GND

1A3

1A4

V

CC

1A5

1A6

GND

1A7

1A8

2A1

2A2

GND

2A3

2A4

V

CC

2A5

2A6

GND

2A7

2A8

2DIR

1OE

1B1

1B2

GND

1B3

1B4

BIAS V

CC

1B5

1B6

GND

1B7

1B8

2B1

2B2

GND

2B3

2B4

V

REF

2B5

2B6

GND

2B7

2B8

2OE

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SN74GTLPH16945VR | 16-BIT LVTTL-TO-GTLP BUS TRANSCEIVER |

| SN74H102 | AND-GATE J-K NEGATIVE-EDGE-TRIGGERED FLIP-FLOPS WITH PRESET AND CLEAR |

| SN74H102J | AND-GATE J-K NEGATIVE-EDGE-TRIGGERED FLIP-FLOPS WITH PRESET AND CLEAR |

| SN74H102N | AND-GATE J-K NEGATIVE-EDGE-TRIGGERED FLIP-FLOPS WITH PRESET AND CLEAR |

| SN74HC148DWR | 8-LINE TO 3-LINE PRIORITY ENCODERS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SN74GTLPH16945VR | 功能描述:總線收發(fā)器 16bit LVTTL-GTLP RoHS:否 制造商:Fairchild Semiconductor 邏輯類型:CMOS 邏輯系列:74VCX 每芯片的通道數(shù)量:16 輸入電平:CMOS 輸出電平:CMOS 輸出類型:3-State 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時間:6.2 ns 電源電壓-最大:2.7 V, 3.6 V 電源電壓-最小:1.65 V, 2.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

| SN74GTLPH306DGVR | 功能描述:轉(zhuǎn)換 - 電壓電平 8bit LVTTL-GTLP RoHS:否 制造商:Micrel 類型:CML/LVDS/LVPECL to LVCMOS/LVTTL 傳播延遲時間:1.9 ns 電源電流:14 mA 電源電壓-最大:3.6 V 電源電壓-最小:3 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:MLF-8 |

| SN74GTLPH306DW | 功能描述:轉(zhuǎn)換 - 電壓電平 8-Bit LVTTL-to-GTLP Bus Transceiver RoHS:否 制造商:Micrel 類型:CML/LVDS/LVPECL to LVCMOS/LVTTL 傳播延遲時間:1.9 ns 電源電流:14 mA 電源電壓-最大:3.6 V 電源電壓-最小:3 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:MLF-8 |

| SN74GTLPH306DWG4 | 功能描述:轉(zhuǎn)換 - 電壓電平 8B LVTTL to GTLP Bus Transceiver RoHS:否 制造商:Micrel 類型:CML/LVDS/LVPECL to LVCMOS/LVTTL 傳播延遲時間:1.9 ns 電源電流:14 mA 電源電壓-最大:3.6 V 電源電壓-最小:3 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:MLF-8 |

| SN74GTLPH306DWR | 功能描述:轉(zhuǎn)換 - 電壓電平 8bit LVTTL-GTLP RoHS:否 制造商:Micrel 類型:CML/LVDS/LVPECL to LVCMOS/LVTTL 傳播延遲時間:1.9 ns 電源電流:14 mA 電源電壓-最大:3.6 V 電源電壓-最小:3 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:MLF-8 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。

- VIP會員服務(wù) |

- 廣告服務(wù) |

- 付款方式 |

- 聯(lián)系我們 |

- 招聘銷售 |

- 免責條款 |

- 網(wǎng)站地圖