- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374861 > SN74ACT3641PQ (Texas Instruments, Inc.) Low-Voltage Quad 2-Input OR Gate with 5V-Tolerant Inputs, Pb-free; Package: SOEIAJ-14; No of Pins: 14; Container: Tape and Reel; Qty per Container: 2000 PDF資料下載

參數(shù)資料

| 型號: | SN74ACT3641PQ |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | Low-Voltage Quad 2-Input OR Gate with 5V-Tolerant Inputs, Pb-free; Package: SOEIAJ-14; No of Pins: 14; Container: Tape and Reel; Qty per Container: 2000 |

| 中文描述: | 1024】36時鐘先入先出存儲器 |

| 文件頁數(shù): | 16/26頁 |

| 文件大小: | 379K |

| 代理商: | SN74ACT3641PQ |

SN74ACT3641

1024

×

36

CLOCKED FIRST-IN, FIRST-OUT MEMORY

SCAS338C – JANUARY 1994 – REVISED OCTOBER 1997

16

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

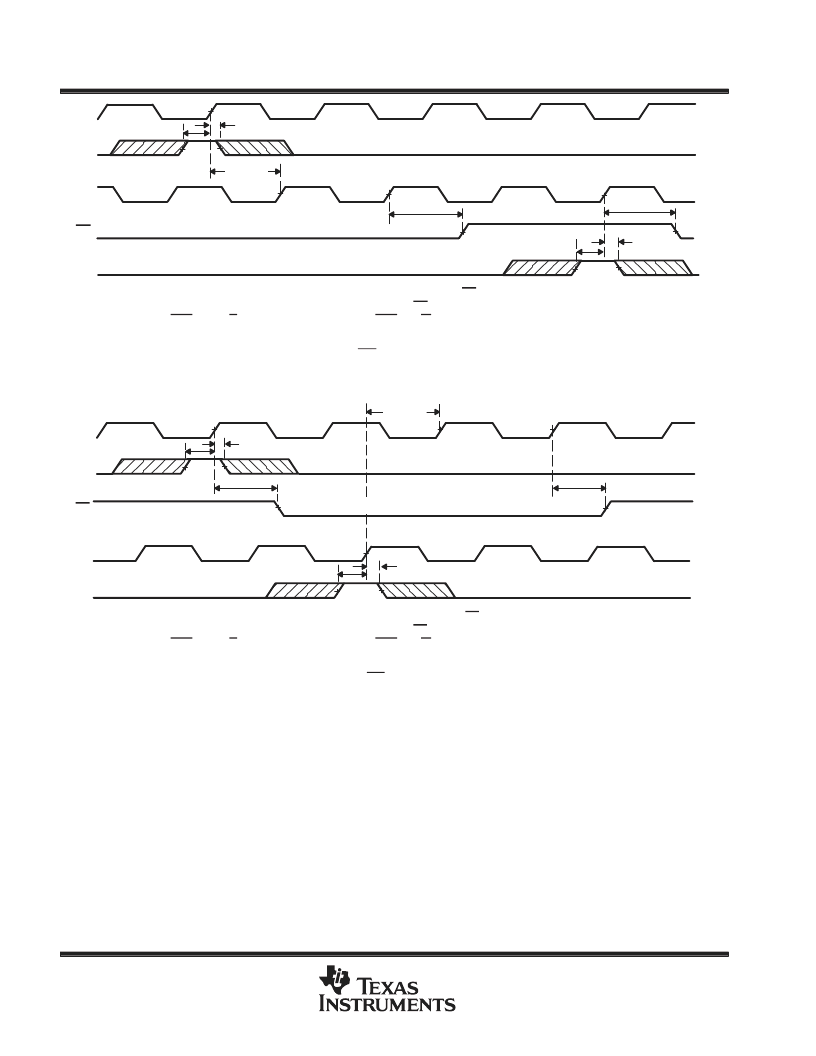

(X + 1) Words in FIFO

ììììì

ììììì

CLKA

AE

ENB

ENA

tsu(EN1)

tsk(2)

tpd(C-AE)

X Words in FIFO

1

CLKB

2

tpd(C-AE)

th(EN1)

ììììì

ììììì

tsk(2) is the minimum time between a rising CLKA edge and a rising CLKB edge for AE to transition high in the next CLKB cycle. If the time

between the rising CLKA edge and rising CLKB edge is less than tsk(2), AE can transition high one CLKB cycle later than shown.

NOTE A: FIFO write (CSA = L, W/RA = H, MBA = L), FIFO read (CSB = L, W/RB = H, MBB = L)

Figure 8. Timing for AE When FIFO Is Almost Empty

(1024 – Y) Words in FIFO

tpd(C-AF)

ììììì

ììììì

CLKA

AF

ENB

ENA

tsu(EN1)

th(EN1)

[1024 – (Y + 1)] Words in FIFO

th(EN1)

tsk(2)

1

2

ììììì

ììììì

CLKB

tsk(2) is the minimum time between a rising CLKA edge and a rising CLKB edge for AF to transition high in the next CLKA cycle. If the time

between the rising CLKB edge and rising CLKA edge is less than tsk(2), AF can transition high one CLKA cycle later than shown.

NOTE A: FIFO write (CSA = L, W/RA = H, MBA = L), FIFO read (CSB = L, W/RB = H, MBB = L)

Figure 9. Timing for AF When FIFO Is Almost Full

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SN74ACT3651PCB | Low-Voltage CMOS Octal Transparent Latch; Package: TSSOP 20 LEAD; No of Pins: 20; Container: Rail; Qty per Container: 75 |

| SN74ACT3651PQ | Low-Voltage CMOS Octal Transparent Latch; Package: TSSOP 20 LEAD; No of Pins: 20; Container: Tape and Reel; Qty per Container: 2500 |

| SN74ACT373DB | OCTAL D-TYPE TRANSPARENT LATCHES WITH 3-STATE OUTPUTS |

| SN54ACT373FK | OCTAL D-TYPE TRANSPARENT LATCHES WITH 3-STATE OUTPUTS |

| SN54ACT373J | OCTAL D-TYPE TRANSPARENT LATCHES WITH 3-STATE OUTPUTS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SN74ACT3651-15PCB | 功能描述:先進先出 2048 x 36 synch 先進先出 Memory RoHS:否 制造商:IDT 電路數(shù)量: 數(shù)據(jù)總線寬度:18 bit 總線定向:Unidirectional 存儲容量:4 Mbit 定時類型:Synchronous 組織:256 K x 18 最大時鐘頻率:100 MHz 訪問時間:10 ns 電源電壓-最大:3.6 V 電源電壓-最小:6 V 最大工作電流:35 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-80 封裝: |

| SN74ACT3651-15PQ | 功能描述:先進先出 2048 x 36 synch 先進先出 Memory RoHS:否 制造商:IDT 電路數(shù)量: 數(shù)據(jù)總線寬度:18 bit 總線定向:Unidirectional 存儲容量:4 Mbit 定時類型:Synchronous 組織:256 K x 18 最大時鐘頻率:100 MHz 訪問時間:10 ns 電源電壓-最大:3.6 V 電源電壓-最小:6 V 最大工作電流:35 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-80 封裝: |

| SN74ACT3651-20PBC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| SN74ACT3651-20PCB | 功能描述:先進先出 2048 x 36 synch 先進先出 Memory RoHS:否 制造商:IDT 電路數(shù)量: 數(shù)據(jù)總線寬度:18 bit 總線定向:Unidirectional 存儲容量:4 Mbit 定時類型:Synchronous 組織:256 K x 18 最大時鐘頻率:100 MHz 訪問時間:10 ns 電源電壓-最大:3.6 V 電源電壓-最小:6 V 最大工作電流:35 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-80 封裝: |

| SN74ACT3651-20PQ | 功能描述:先進先出 2048 x 36 synch 先進先出 Memory RoHS:否 制造商:IDT 電路數(shù)量: 數(shù)據(jù)總線寬度:18 bit 總線定向:Unidirectional 存儲容量:4 Mbit 定時類型:Synchronous 組織:256 K x 18 最大時鐘頻率:100 MHz 訪問時間:10 ns 電源電壓-最大:3.6 V 電源電壓-最小:6 V 最大工作電流:35 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-80 封裝: |

發(fā)布緊急采購,3分鐘左右您將得到回復。