- 您現(xiàn)在的位置:買(mǎi)賣IC網(wǎng) > PDF目錄374749 > SDA9380-B21 (MICRONAS SEMICONDUCTOR HOLDING AG) EDDC Enhanced Deflection Controller and RGB Processor PDF資料下載

參數(shù)資料

| 型號(hào): | SDA9380-B21 |

| 廠商: | MICRONAS SEMICONDUCTOR HOLDING AG |

| 元件分類: | 消費(fèi)家電 |

| 英文描述: | EDDC Enhanced Deflection Controller and RGB Processor |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

| 封裝: | PLASTIC, MQFP-64 |

| 文件頁(yè)數(shù): | 19/72頁(yè) |

| 文件大小: | 366K |

| 代理商: | SDA9380-B21 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)當(dāng)前第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)

SDA 9380 - B21

Preliminary Data Sheet

System description

Micronas

5-11

2001-01-29

5.2

Circuit description

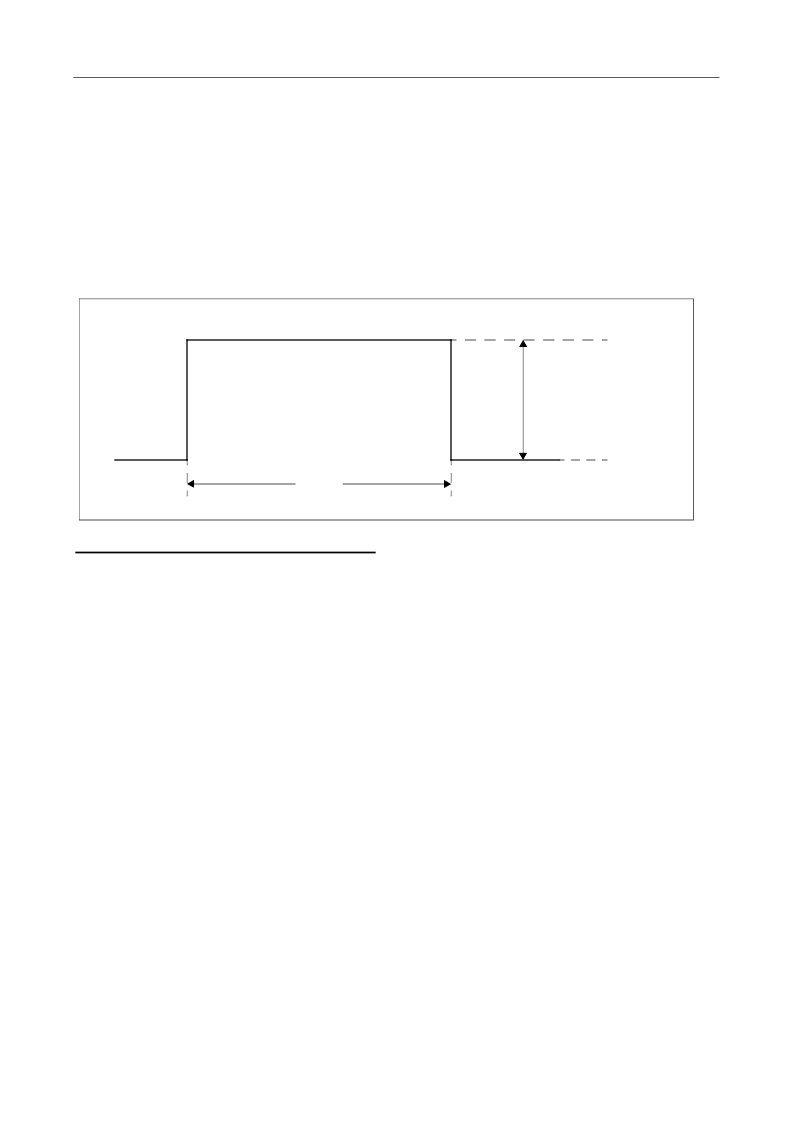

The HSYNC is reference for a numeric PLL. This PLL generates a clock which is phase locked to

the incoming horizontal sync pulse and exactly 864 times faster than the horizontal frequency. The

polarity of the external horizontal sync pulses may be positive (see figure below) or negative. In

case of negative polarity the incoming HSYNC signal is automatically inverted for an easier applica-

tion in VGA or SVGA mode.

Incoming signal HSYNC (internal clock)

Pulse width t

w

for I

2

C-bus Bit ’HSWMI’=0:

1.5

μ

s ... 4.5

μ

s (High or Low level)

3.0

μ

s ... 9.0

μ

s (High or Low level)

Pulse width t

w

for I

2

C-bus Bit ’HSWMI’=1:

0.8

μ

s ... 4.5

μ

s (High or Low level)

1.7

μ

s ... 9.0

μ

s (High or Low level)

FH1_2 = High

FH1_2 = Low

FH1_2 = High

FH1_2 = Low

(The specified pulse width depends on the I2C-bus bits INCR4...INCR0 rsp. PLL clock frequency.

The above values are valid for INCR = 6. For higher INCR values the allowed pulse width is

decreasing proportional to the increasing PLL clock frequency.)

The described input signal is first applied to an A/D converter. Conversion takes place with 7 bits

and a nominal frequency of 27 MHz. The digital PLL uses a low pass filter to obtaine defined slopes

for further measurements (PAL/NTSC applications). In addition the actual high and low level of the

signal as well as a threshold value is evaluated and used to calculate the phase error between inter-

nal clock and external horizontal sync pulse. By means of digital PI filtering an increment is gained

from this. The PI filter can be set by the I

2

C-bus VCR bit so that the lock-in behaviour of the PLL is

optimal in relation to either the TV or VCR mode. Moreover it is possible to adapt the nominal fre-

quency by means of 5 I

2

C-bus bits (INCR4..INCR0) to different horizontal frequencies. An additional

bus bit GENMOD offers the possibility to use the PLL as a frequency generator which frequency is

controlled by the INCR bits.

V

HSmin

V

HSpp

V

HSmax

t

W

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SDA9388X | Single-Chip Picture in Picture IC |

| SDA9400 | Scan Rate Converter using Embedded DRAM Technology Units |

| SDA9410-B13 | Display Processor and Scan Rate Converter using Embedded DRAM Technology Units |

| SDA9415-B13 | Display Processor and Scan Rate Converter |

| SDA9488X | Cost-effective Picture-In-Picture ICs |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SDA9388X | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:Single-Chip Picture in Picture IC |

| SDA9400 | 制造商:MICRONAS 制造商全稱:MICRONAS 功能描述:Scan Rate Converter using Embedded DRAM Technology Units |

| SDA9401 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Scan Rate Converter using Embedded DRAM Technology Units |

| SDA9410-B13 | 制造商:MICRONAS 制造商全稱:MICRONAS 功能描述:Display Processor and Scan Rate Converter using Embedded DRAM Technology Units |

| SDA9415-B13 | 制造商:MICRONAS 制造商全稱:MICRONAS 功能描述:Display Processor and Scan Rate Converter |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。