- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄296691 > NHI-1598ET/883 (NATIONAL HYBRID INC) 2 CHANNEL(S), MIL-STD-1553 CONTROLLER, CPGA69 PDF資料下載

參數(shù)資料

| 型號: | NHI-1598ET/883 |

| 廠商: | NATIONAL HYBRID INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 2 CHANNEL(S), MIL-STD-1553 CONTROLLER, CPGA69 |

| 封裝: | 1.100 X 1.100 INCH, CERAMIC, PLUG IN, PGA-69 |

| 文件頁數(shù): | 21/89頁 |

| 文件大?。?/td> | 569K |

| 代理商: | NHI-1598ET/883 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁當(dāng)前第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁

-

27

LOCAL_ DYNAMIC_ BUS_ SELECTION

Bits: 3

BC

0 = Message bus unchanged after successful Local Retry.

1 = Automatically switch message to alternate bus in BC Control Word after successful retry on

alternate bus due to Local Retry option.

INHIBIT SOFT_ ADR

Bits: 2

RT

0 = Bits (15: 11) of Basic Status Register set the RT Address when a Write Operation to that

register is performed. The Hard Wired Address sets the RT Address at RESET.

1 = Prevents software change of RT Address when writing to the Basic Status Register.

Bits (15: 11) of Basic Status Register are “Don’t Care”. Only the Hard Wired Address sets the

RT Address at RESET.

CONVERT BUSY BIT

Bits: 1

RT

0 = BUSY Bit is compliant with Mil- Std- 1553B.

1 = Converts BUSY Bit to Non- 1553B operation. BUSY Bit becomes a standard bit with no

special functionality. BUSY Bit is not set during software reset or MODE CODE_ 08 RESET.

SEP_ BCST_ TABLES

Bits: 0

RT

0 = Broadcast messages use the same pointers as receive message:. therefore, receive and

broadcast messages are stored in the same data tables. The BCST bit in the tag word is

used to differentiate between the two message types.

1 = An additional 30 pointers are activated which puts receive and broadcast messages in

separate data tables.

4.2.25

FRAME "A" POINTER

Address: 13

R/ W

BC/ MT

BLOCK "A" START

This register contains the 16 bit FRAME "A" POINTER. This is the address of the active message

list to be used by the BC or the MESSAGE MONITOR for FRAME "A".

In the WORD MONITOR, this register contains the 16 bit start address of BLOCK "A".

4.2.26

FRAME "A" LENGTH

Address: 14

R/ W

BC/ MT

BLOCK "A" END

In the BC and MESSAGE MONITOR modes, this register specifies the number of messages in

FRAME "A" message list and several END- OF- FRAME options.

In the WORD MONITOR, this register contains the 16 bit end address of BLOCK "A".

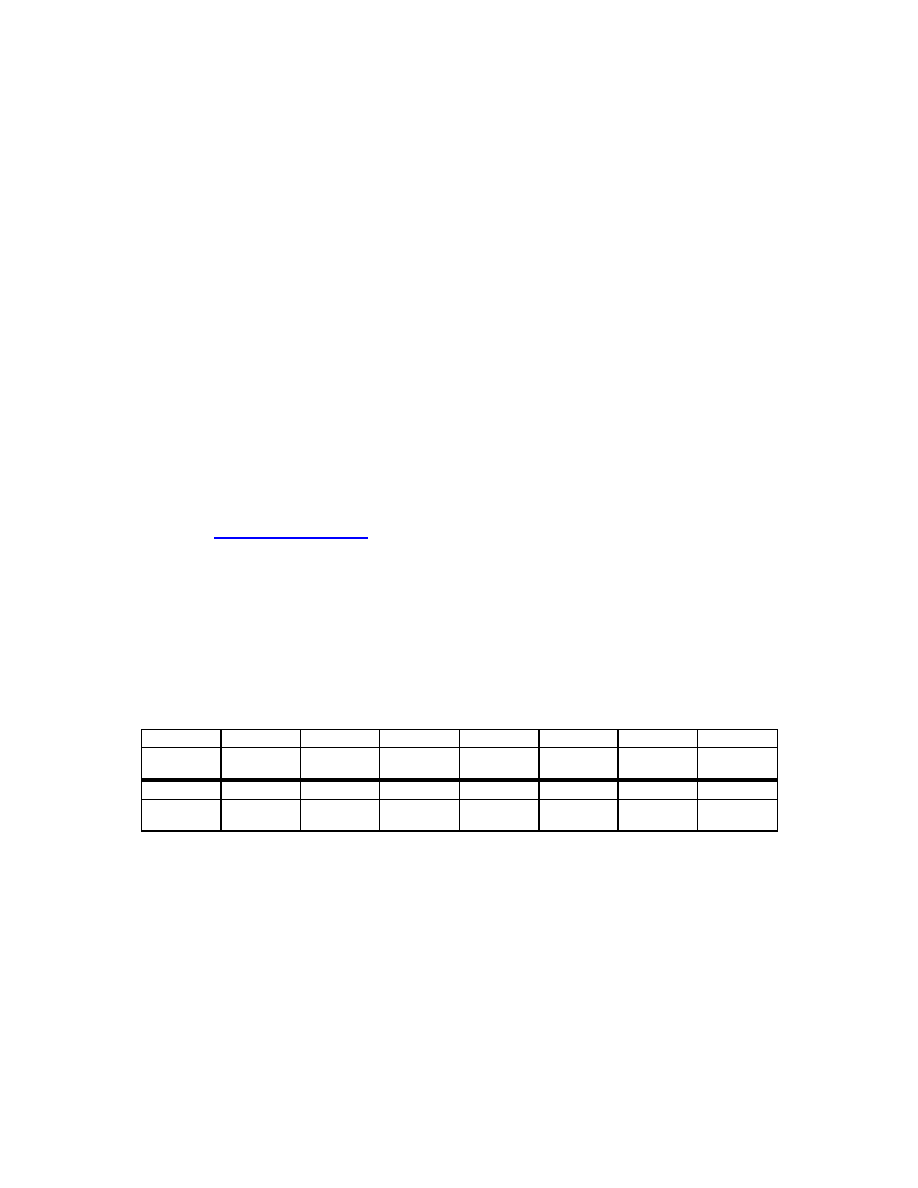

15

14

13

12

11

10

9

8

RSVD

END OF A

INT

STAT SET

STOP A

FRAME A

ERR STOP

FRAME A

END OPT1

FRAME A

END OPT0

FRAME A

LEN9

FRAME A

LEN8

7

6

5

4

3

2

1

0

FRAME A

LEN7

FRAME A

LEN6

FRAME A

LEN5

FRAME A

LEN4

FRAME A

LEN3

FRAME A

LEN2

FRAME A

LEN1

FRAME A

LEN0

Note: In the Message Monitor mode Bits 12 and 13 are reserved and always read 0.

END OF A INT

Bits: 14

BC/ MT

1 = The BC or the Message Monitor will interrupt when End of FRAME "A" is reached.

0 = End of Frame WILL NOT cause an interrupt.

STAT SET STOP A

Bits: 13

BC

1 = If any BC message in the frame causes a status bit set condition, then BC will stop at the end

of the current frame and go off line.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| NJG1145UA2 | 90 MHz - 2150 MHz RF/MICROWAVE WIDE BAND LOW POWER AMPLIFIER |

| NJG1515AVB2 | RF/MICROWAVE TRANSFER SWITCH |

| NJG1667MD7 | 1000 MHz - 2500 MHz RF/MICROWAVE SGL POLE FIVE THROW SWITCH, 0.8 dB INSERTION LOSS |

| NJU6319DC | 6.25 MHz, OTHER CLOCK GENERATOR, UUC6 |

| NJU6338BE | 17.5 MHz, OTHER CLOCK GENERATOR, PDSO8 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| NHI21PKZ0 | 制造商:EATON MOELLER 功能描述:Contactor 制造商:EATON MOELLER 功能描述:CONTACTOR; Contact Configuration:3PST-2NO / SPST-NC; IP / NEMA Rating:IP20; No. of Poles:3 ;RoHS Compliant: Yes |

| NHI21-PKZ0 | 制造商:Moeller Electric Corporation 功能描述:Auxiliary Switch Nhi-Pkz0 |

| NHI21-PKZO | 制造商:EATON MOELLER 功能描述:CONTACT BLOCK 2NO+1NC |

| NHI350AM2 S LJ3S | 制造商:Intel 功能描述:Ethernet CTLR Single Chip 10Mbps/100Mbps/1000Mbps 3.3V 256-Pin BGA 制造商:Intel 功能描述:POWERVILLE, ETHERNET CONTROLLER I350-AM2 - Trays |

| NHI350AM2 S LJ3S | 制造商:Intel 功能描述:Ethernet ICs Controller IEEE 10/ 100/1000 Mbps BGA256 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。