- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359234 > MT9045AN (ZARLINK SEMICONDUCTOR INC) T1/E1/OC3 System Synchronizer PDF資料下載

參數(shù)資料

| 型號: | MT9045AN |

| 廠商: | ZARLINK SEMICONDUCTOR INC |

| 元件分類: | 通信及網(wǎng)絡 |

| 英文描述: | T1/E1/OC3 System Synchronizer |

| 中文描述: | SPECIALTY TELECOM CIRCUIT, PDSO48 |

| 封裝: | 0.300 INCH, MO-118AA, SSOP-48 |

| 文件頁數(shù): | 7/34頁 |

| 文件大小: | 495K |

| 代理商: | MT9045AN |

第1頁第2頁第3頁第4頁第5頁第6頁當前第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁

MT9045

Data Sheet

7

Zarlink Semiconductor Inc.

Digital Phase Lock Loop (DPLL)

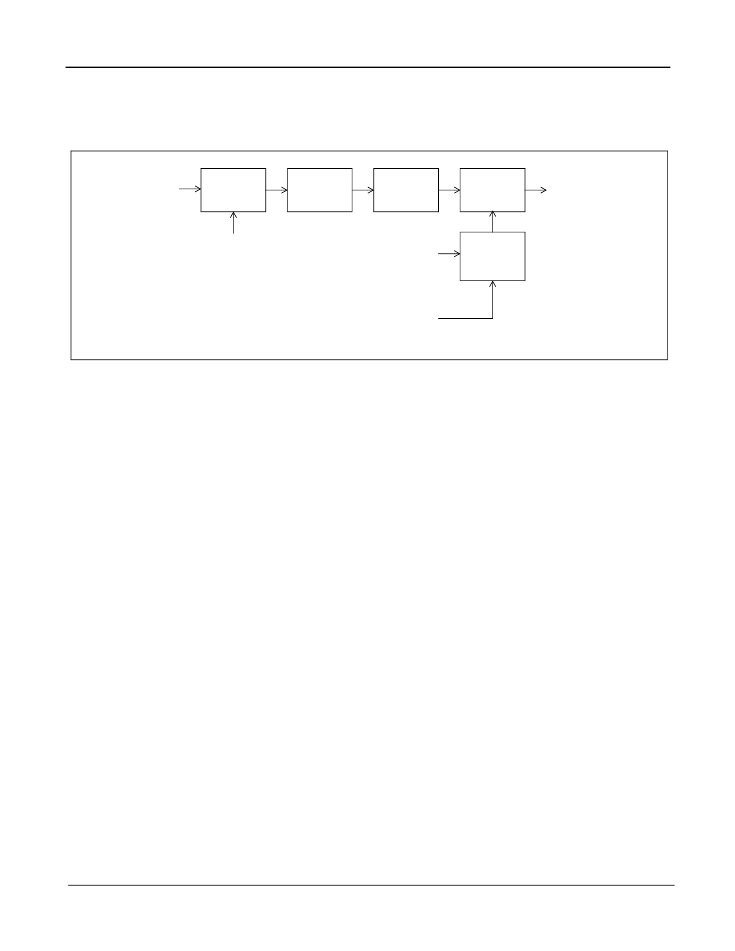

As shown in Figure 4, the DPLL of the MT9045 consists of a Phase Detector, Limiter, Loop Filter, Digitally

Controlled Oscillator, and a Control Circuit.

Figure 4 - DPLL Block Diagram

Phase Detector

- the Phase Detector compares the virtual reference signal from the TIE Corrector circuit with the

feedback signal from the Frequency Select MUX circuit, and provides an error signal corresponding to the phase

difference between the two. This error signal is passed to the Limiter circuit. The Frequency Select MUX allows the

proper feedback signal to be externally selected (e.g., 8kHz, 1.544MHz, 2.048MHz or 19.44MHz).

Limiter

- the Limiter receives the error signal from the Phase Detector and ensures that the DPLL responds to all

input transient conditions with a maximum output phase slope of 5ns per 125us. This is well within the maximum

phase slope of 7.6ns per 125us or 81ns per 1.326ms specified by AT&T TR62411 and Bellcore GR-1244-CORE,

respectively.

Loop Filter

- the Loop Filter is similar to a first order low pass filter with a 1.9 Hz cutoff frequency for all four

reference frequency selections (8kHz, 1.544MHz, 2.048MHz or 19.44MHz). This filter ensures that the jitter transfer

requirements in ETS 300 011 and AT&T TR62411 are met.

Control Circuit

- the Control Circuit uses status and control information from the State Machine and the Input

Impairment Circuit to set the mode of the DPLL. The three possible modes are Normal, Holdover and Freerun.

Digitally Controlled Oscillator (DCO)

- the DCO receives the limited and filtered signal from the Loop Filter, and

based on its value, generates a corresponding digital output signal. The synchronization method of the DCO is

dependent on the state of the MT9045.

In Normal Mode, the DCO provides an output signal which is frequency and phase locked to the selected input

reference signal.

In Holdover Mode, the DCO is free running at a frequency equal to the last (less 30ms to 60ms) frequency the DCO

was generating while in Normal Mode.

In Freerun Mode, the DCO is free running with an accuracy equal to the accuracy of the OSCi 20MHz source.

Lock Indicator

- If the PLL is in frequency lock (frequency lock means the center frequency of the PLL is identical

to the line frequency), and the input phase offset is small enough such that no phase slope limiting is exhibited, then

the lock signal will be set high. For specific Lock Indicator design recommendations see the Applications - Lock

Indicator section.

Control

Circuit

State Select

from

Input Impairment Monitor

State Select

from

State Machine

Feedback Signal

from

Frequency Select MUX

DPLL Reference

to

Output Interface Circuit

Virtual Reference

from

TIE Corrector

Limiter

Loop Filter

Digitally

Controlled

Oscillator

Phase

Detector

相關PDF資料 |

PDF描述 |

|---|---|

| MT9046 | T1/E1 System Synchronizer with Holdover |

| MT9046AN | T1/E1 System Synchronizer with Holdover |

| MT90503 | 2048VC AAL1 SAR |

| MT90503AG | CLIP, STRAIN RELIEF, 50WAY; For use with:820 Series Tripolarized Wiremount Sockets; Ways, No. of:50; Material:Metal; Connector type:Strain Relief RoHS Compliant: Yes |

| MT90520 | 8-Port Primary Rate Circuit Emulation AAL1 SAR |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| MT9045AN1 | 制造商:Microsemi Corporation 功能描述:FRAMER E1/OC3/T1 3.3V 48SSOP - Rail/Tube 制造商:Microsemi Corporation 功能描述:T1/E1/OC3 SYSTEM SYNCHRONIZER |

| MT9045ANR1 | 制造商:Microsemi Corporation 功能描述:FRAMER E1/OC3/T1 3.3V 48SSOP - Tape and Reel 制造商:Microsemi Corporation 功能描述:iB FREE T1/E1/OC3 SYSTEM SYNCHRONIZER 制造商:Zarlink Semiconductor Inc 功能描述:FRAMER E1/OC3/T1 3.3V 48SSOP - Tape and Reel |

| MT9046 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:SONET/SDH Clock Multiplier PLL |

| MT9046AN | 制造商:Microsemi Corporation 功能描述: |

| MT9046AN1 | 制造商:Microsemi Corporation 功能描述:FRAMER E1 /T1 3.3V 48SSOP - Rail/Tube 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC SYNCHRONIZER T1/E1 48SSOP 制造商:Microsemi Corporation 功能描述:IC SYNCHRONIZER T1/E1 48SSOP |

發(fā)布緊急采購,3分鐘左右您將得到回復。