- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359234 > MT9043AN48PINSSOP (Zarlink Semiconductor Inc.) T1/E1 System Synchronizer PDF資料下載

參數(shù)資料

| 型號: | MT9043AN48PINSSOP |

| 廠商: | Zarlink Semiconductor Inc. |

| 英文描述: | T1/E1 System Synchronizer |

| 中文描述: | T1/E1的系統(tǒng)同步 |

| 文件頁數(shù): | 5/29頁 |

| 文件大小: | 453K |

| 代理商: | MT9043AN48PINSSOP |

第1頁第2頁第3頁第4頁當前第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁

MT9043

Data Sheet

5

Zarlink Semiconductor Inc.

Time Interval Error (TIE) Corrector Circuit

The TIE corrector circuit, when enabled, prevents a step change in phase on the input reference signals (PRI or

SEC) from causing a step change in phase at the input of the DPLL block of Figure 1.

During reference input rearrangement, such as during a switch from the primary reference (PRI) to the secondary

reference (SEC), a step change in phase on the input signals will occur. A phase step at the input of the DPLL

would lead to unacceptable phase changes in the output signal.

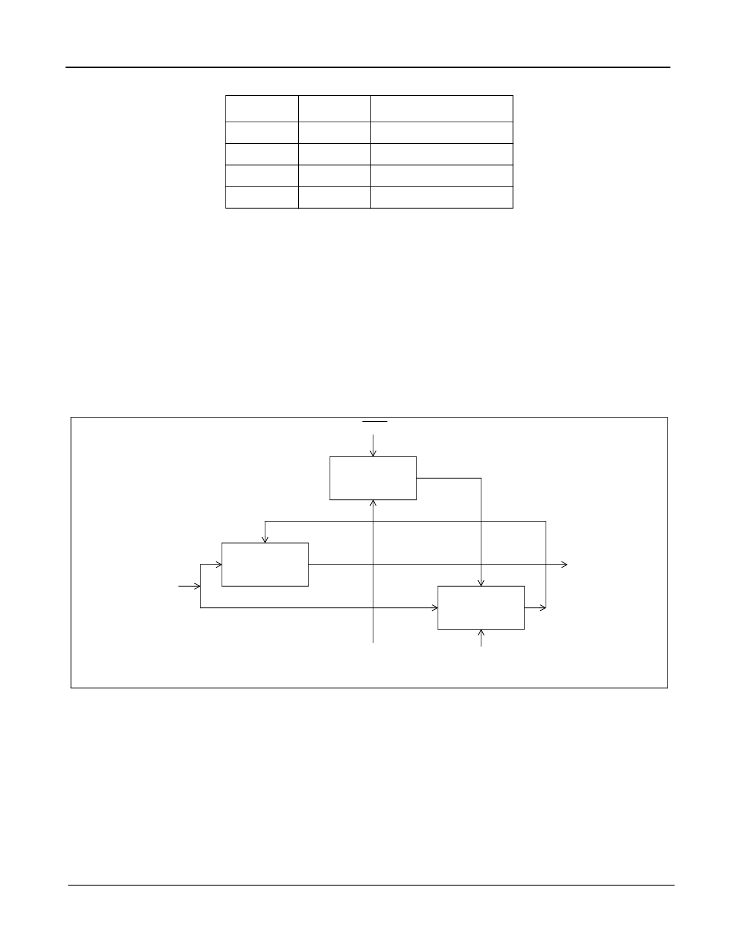

As shown in Figure 3, the TIE Corrector Circuit receives one of the two reference (PRI or SEC) signals, passes the

signal through a programmable delay line, and uses this delayed signal as an internal virtual reference, which is

input to the DPLL. Therefore, the virtual reference is a delayed version of the selected reference.

Figure 3 - TIE Corrector Circuit

During a switch from one reference to the other, the State Machine first changes the mode of the device

from Normal to Freerun. The Compare Circuit then measures the phase delay between the current phase

(feedback signal) and the phase of the new reference signal. This delay value is passed to the Programmable

Delay Circuit (See Figure 3). The state machine then returns the device to Normal Mode and the DPLL begins

using the new virtual reference signal. The difference between the phase position of the new virtual reference and

the previous reference is less than 1

μ

s.

Since internal delay circuitry maintains the alignment between the old virtual reference and the new virtual

reference, a phase error may exist between the selected input reference signal and the output signal of the DPLL.

This phase error is a function of the difference in phase between the two input reference signals during reference

FS2

FS1

Input Frequency

0

0

19.44MHz

0

1

8kHz

1

0

1.544MHz

1

1

2.048MHz

Table 1 - Input Frequency Selection

Programmable

Delay Circuit

Control Signal

Delay Value

TCLR

Resets Delay

Compare

Circuit

TIE Corrector

Enable

from

State Machine

Control

Circuit

Feedback

Signal from

Frequency

Select MUX

PRI or SEC

from

Reference

Select Mux

Virtual

Reference

to DPLL

相關PDF資料 |

PDF描述 |

|---|---|

| MT9045 | T1/E1/OC3 System Synchronizer |

| MT9045AN | T1/E1/OC3 System Synchronizer |

| MT9046 | T1/E1 System Synchronizer with Holdover |

| MT9046AN | T1/E1 System Synchronizer with Holdover |

| MT90503 | 2048VC AAL1 SAR |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| MT9043ANR1 | 制造商:Microsemi Corporation 功能描述:FRAMER E1 /T1 3.3V 48SSOP - Tape and Reel 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC SYNCHRONIZER T1/E1 48SSOP 制造商:Microsemi Corporation 功能描述:IC SYNCHRONIZER T1/E1 48SSOP |

| MT9044 | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:T1/E1/OC3 System Synchronizer |

| MT9044AL | 制造商:Microsemi Corporation 功能描述:FRAMER E1/OC3/T1 5V 44MQFP - Trays 制造商:Zarlink Semiconductor Inc 功能描述:FRAMER E1/OC3/T1 5V 44MQFP - Trays |

| MT9044AL1 | 制造商:Microsemi Corporation 功能描述:FRAMER E1/OC3/T1 5V 44MQFP - Trays |

| MT9044AP | 制造商:Microsemi Corporation 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復。