- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄53728 > MK2702STR 27 MHz, OTHER CLOCK GENERATOR, PDSO8 PDF資料下載

參數(shù)資料

| 型號: | MK2702STR |

| 元件分類: | 時鐘產(chǎn)生/分配 |

| 英文描述: | 27 MHz, OTHER CLOCK GENERATOR, PDSO8 |

| 封裝: | SOIC-8 |

| 文件頁數(shù): | 3/4頁 |

| 文件大小: | 42K |

| 代理商: | MK2702STR |

MK2702

PLL Audio Clock Synthesizer

MDS2702A

3

Revision 12237

Printed 12/23/97

MicroClock Division of ICS1271 Parkmoor Ave.San JoseCA95126(408)295-9800tel(408)295-9818fax

PRELIMINARY INFORMATION

ICRO

CLOCK

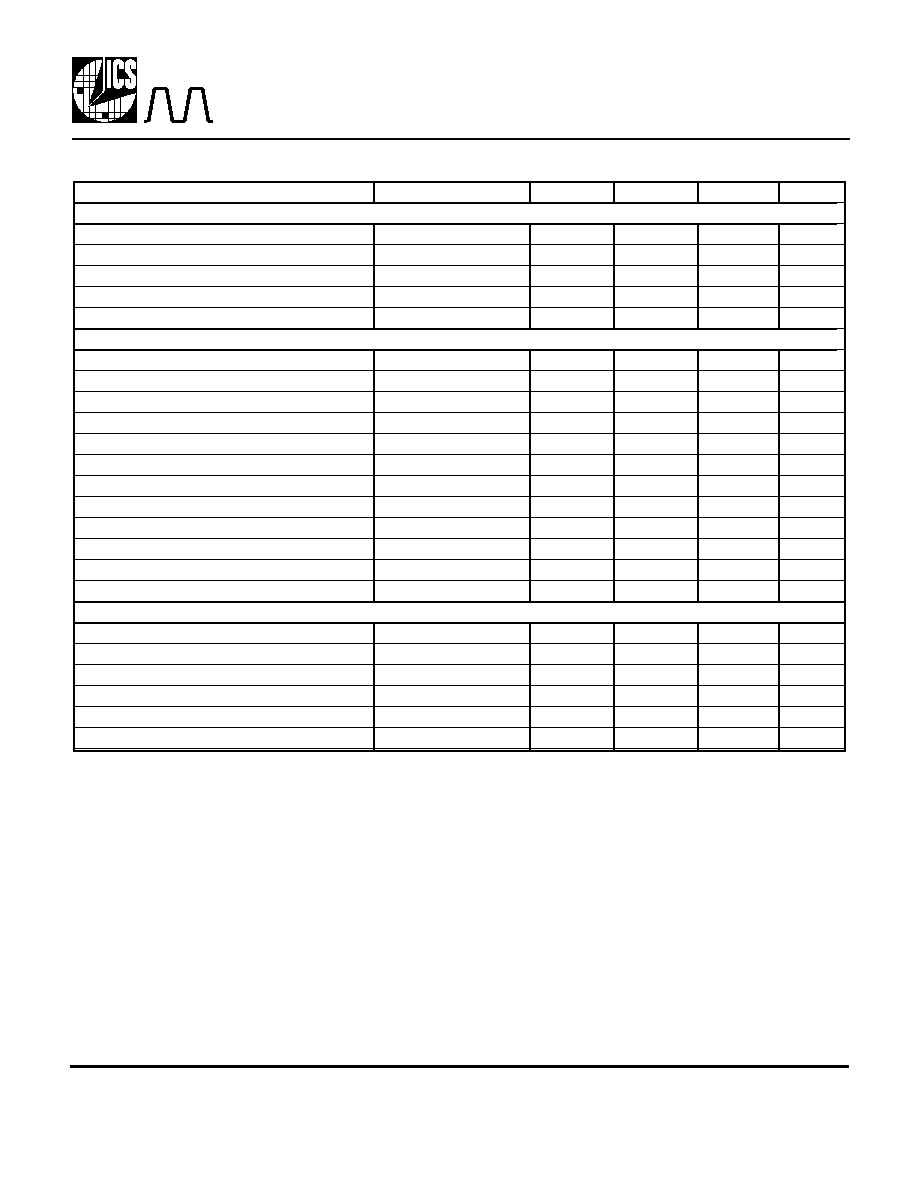

Parameter

Conditions

Minimum

Typical

Maximum

Units

ABSOLUTE MAXIMUM RATINGS (note 1)

Supply voltage, VDD

Referenced to GND

7

V

Inputs and Clock Outputs

Referenced to GND

-0.5

VDD+0.5

V

Ambient Operating Temperature

0

70

°C

Soldering Temperature

Max of 10 seconds

260

°C

Storage temperature

-65

150

°C

DC CHARACTERISTICS (VDD = 5.0V unless noted)

Operating Voltage, VDD

3.13

5.50

V

Input High Voltage, VIH, X1 pin only

(VDD/2)+1

VDD/2

V

Input Low Voltage, VIL, X1 pin only

VDD/2

(VDD/2)-1

V

Input High Voltage, VIH

2

V

Input Low Voltage, VIL

0.8

V

Output High Voltage, VOH

IOH=-25mA

2.4

V

Output Low Voltage, VOL

IOL=25mA

0.4

V

Output High Voltage, VOH, CMOS level

IOH=-8mA

VDD-0.4

V

Operating Supply Current, IDD

No Load

25

mA

Short Circuit Current

Each output

±100

mA

Input Capacitance

SEL

5

pF

Frequency synthesis error

All clocks

0

ppm

AC CHARACTERISTICS (VDD = 5.0V unless noted)

Input Crystal Frequency

27.00

MHz

Input Crystal Accuracy

±30

ppm

Output Clock Rise Time

0.8 to 2.0V

1.5

ns

Output Clock Fall Time

2.0 to 0.8V

1.5

ns

Output Clock Duty Cycle

At 1.4V

40

60

%

Maximum Absolute Jitter, short term

150

ps

Electrical Specifications

Notes:

1. Stresses beyond those listed under Absolute Maximum Ratings could cause permanent damage to the device. Prolonged

exposure to levels above the operating limits but below the Absolute Maximums may affect device reliability.

External Components

The MK2702 requires a minimum number of external components for proper operation. For a crystal input,

one load capacitor should be connected from each of the X1 and X2 pins to ground. The value (in pF) of

each crystal load capacitor should equal (CL-6)*2, where CL is the crystal’s load (correlation) capacitance

in pF. The input crystal must be connected as close to the chip as possible. The input crystal should be a

parallel resonant, fundamental, AT cut 27 MHz. For a clock input, connect to X1 and leave X2

unconnected. Decoupling capacitors of 0.1F should be connected between VDD and GND on pins 2

and 3, as close to the MK2702 as possible. A series termination resistor of 33

may be used for the clock

output.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MK2702SLF | 27 MHz, OTHER CLOCK GENERATOR, PDSO8 |

| MK2702SLF | 27 MHz, OTHER CLOCK GENERATOR, PDSO8 |

| MK2702S | 27 MHz, OTHER CLOCK GENERATOR, PDSO8 |

| MK2702STRLF | 27 MHz, OTHER CLOCK GENERATOR, PDSO8 |

| MK2702STRLF | 27 MHz, OTHER CLOCK GENERATOR, PDSO8 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MK2703 | 制造商:ICS 制造商全稱:ICS 功能描述:PLL Audio Clock Synthesizer |

| MK2703BSILF | 功能描述:時鐘合成器/抖動清除器 PLL AUDIO CLOCK SYNTHESIZER RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| MK2703BSILFTR | 功能描述:時鐘合成器/抖動清除器 PLL AUDIO CLOCK SYNTHESIZER RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| MK2703BSLF | 功能描述:時鐘合成器/抖動清除器 PLL AUDIO CLOCK SYNTHESIZER RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| MK2703BSLFTR | 功能描述:時鐘合成器/抖動清除器 PLL AUDIO CLOCK SYNTHESIZER RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。